賽靈思(Xilinx)今日宣布運用4階脈衝振幅調變(PAM4)傳輸方式的56G收發器技術,開發出以16nm FinFET+為基礎的可編程元件。針對下個世代的線路速率,PAM4解決方案是業界公認最具可擴展性的傳訊協定,將加倍現有基礎架構頻寬,進而協助推動下一波光纖和銅線互聯乙太網路的部署。該公司正在推廣與展示超越一般PAM4可用性的56G技術創新,協助教育供應商和產業生態系成員,使其為技術轉移作好準備。

賽靈思SerDes技術事業群副總裁Ken Chang表示,該公司客戶早已開始期待如何加快下個世代的應用,這讓該公司意識到現在必須提高對56G PAM4技術解決方案的認識,以協助客戶轉移他們的設計。

隨著雲端運算、工業物聯網、軟體定義網路等趨勢持續增長,推動對無限頻寬的需求,技術創新必須擴展至50G、100G、400G連接埠和Terabit介面,以在不增加每位元的成本和功耗下最大化連接埠密度。標準化線路速率是滿足下個世代不斷提高頻寬需求的關鍵。

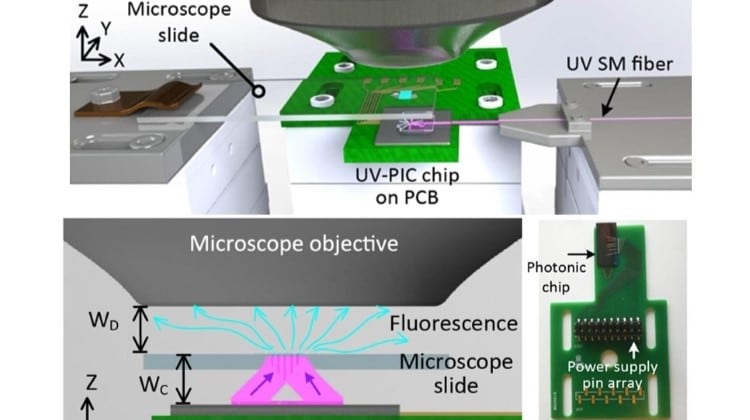

該公司所開發的56G PAM4收發器技術用以突破線路速率、插入損耗及串音等傳統資料傳輸的物理限制。此技術支援晶片對晶片、模組、直接連接纜線或背板應用的銅線和光學互連,將帶來超越Terabit線路卡及400G到Terabit機箱背板的次世代系統設計。

賽靈思網址:www.xilinx.com