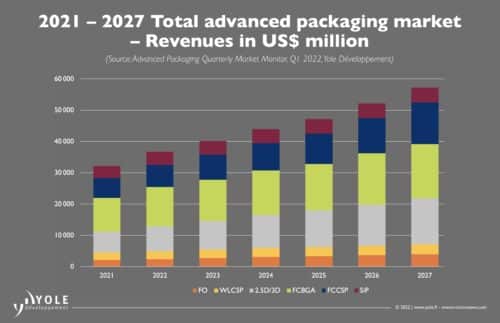

根據Yole市場數據,先進封裝市場正以年複合增長率10%的速度成長,預計2027年達572億美元。IDTechEx更預測,Chiplet技術的市場總價值將在2035年達到4110億美元。然而,這場技術革命的成敗關鍵並不在製造端,而在於能否突破設計工具的根本性限制。

EDA工具正從幕後的輔助角色躍升為先進封裝發展的決定性因素。EDA產業地圖顯示,單顆AI晶片設計需要調用超過50種EDA工具,比傳統晶片增加了300%。

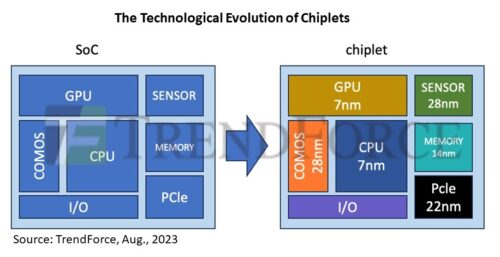

這現象反映的是設計複雜度的幾何級增長:當不同製程節點的晶片需要整合在同一封裝中,當熱管理和機械應力成為關鍵設計變數,當系統級協同最佳化成為必要條件時,傳統EDA工具的設計邏輯已經無法應付。

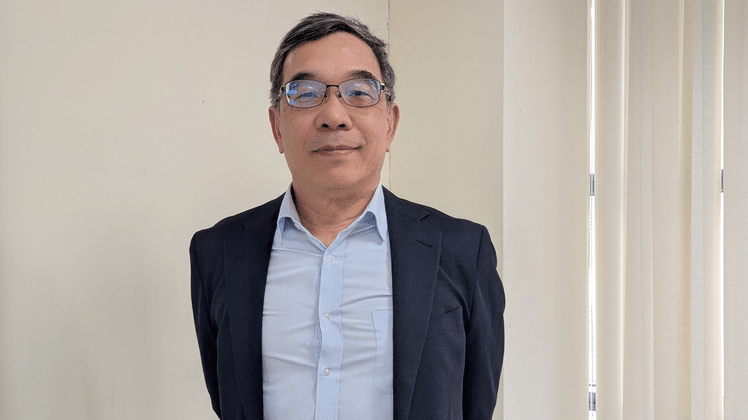

西門子EDA技術經理王誌宏受訪時為我們揭示了解決之道:從AI技術在EDA工具中的深度整合,到系統級協同設計方法論的建立,再到平台化趨勢對產業生態的重新定義,新一代EDA技術正在重構先進封裝的可能性邊界。

設計複雜度躍升 傳統工具面臨三重挑戰

王誌宏深入剖析了EDA工具在先進封裝領域遭遇的技術瓶頸。第一重挑戰來自設計複雜度的指數級提升。傳統單晶片設計雖然複雜,但最終仍是同一製程節點的產物。如今在2.5D、3D IC、Chiplet封裝中,每個元件都是獨立製程的產品,還要加上不同材質的中介層,設計路徑的複雜度比過往提升了至少10倍。

第二重挑戰源於多物理域問題的集中爆發。以前一顆晶片的熱會往上散出,現在把它堆疊在一起時,上面的晶片會被擋住。此外,矽中介層與不同材質間的機械應力問題,在3D堆疊環境下變得極其複雜。熱管理和機械應力已從次要考量躍升為設計成敗的關鍵因素。

第三重挑戰是驗證複雜度的幾何級增長。傳統晶片設計的驗證工具Calibre,面對跨晶片、跨材質、跨封裝層級的複雜架構時,規則撰寫的複雜度呈現爆炸性增長。王誌宏坦言引導工程師去做這件事情的複雜度會變很高。這會直接拖慢設計週期,推高了開發成本。

Intel Ponte Vecchio GPU的成功案例印證了這些挑戰的現實性。這顆整合47個不同Chiplet的處理器,從設計到量產耗時超過四年,其中EDA工具的適配和驗證就占了近三分之一的時間。這樣的開發週期在AI晶片競賽中幾乎是致命的。

系統級協同設計 AI技術成突破關鍵

面對這些挑戰,晶片設計理念正發生根本性轉變:從序列設計轉向並行設計。過去的方法是在最後階段進行驗證和仿真,一旦發現問題就要回頭重來,迭代效率極低。新的設計概念要求設計與驗證並行,在每個階段都引入驗證和模擬,確保無誤後再進入下一階段。

AI技術的深度整合正在重新定義EDA工具的能力邊界。西門子最新的AI平台,用最簡單的概念來解釋就是懂EDA語法的ChatGPT。這個平台能夠自動處理複雜的Calibre語法生成,將原本需要資深工程師數週完成的工作壓縮到數小時。

熱仿真工具的技術革新同樣令人矚目。早期的熱仿真主要針對系統層級,如伺服器或PCB模組。現在這些工具必須深入到IC層級,精確分析3D堆疊結構中每個晶片的熱行為。透過晶片布局優化和散熱路徑設計,工程師能夠在設計早期就解決熱管理問題,避免後期的重大修改。

訊號完整性分析也迎來了突破。王誌宏指出,因為之前都在單晶片裡面做,現在會跨晶片還有跨不同的材質。新的分析工具整合了晶片級和系統級的訊號分析能力,透過實體與頻率的防範技術,將訊號網路分析的精度提升了30%以上。

平台化整合趨勢 產業生態迎來重組

西門子EDA的平台化策略,是以Innovator 3D IC作為中控台,整合從系統技術協同最佳化到具體實現的全流程。這個平台能夠同時處理矽晶片、中介層、封裝基板甚至PCB和BGA的最佳化設計。王誌宏特別提到了成本效益:「有時候上方的Bump稍微排列得好一點,就可以用比較少的層數」,這種優化能夠直接影響中介層的製造成本。

2025年2月18日,西門子與台積電的最新合作案例證明了這種平台化趨勢的重要性。西門子為台積電InFO封裝技術提供經認證的自動化工作流程,採用Innovator3D IC驅動的先進封裝整合解決方案。

Chiplet技術的快速發展正在重新定義產業合作模式。這個龐大市場背後,EDA工具的重要性愈加凸顯。王誌宏認為Chiplet的模組化優勢能夠大幅降低設計風險,他表示,很多常用的方式可以把它做成模組,運用這些早就已經tape out過或驗證過的模組,重複利用。

王誌宏預測未來五年將出現幾個關鍵技術趨勢:晶粒整合將加速發展;高密度3D基層技術將更廣泛應用;矽光子技術將走向成熟;Chiplet將實現大規模商業化應用。每一個趨勢都需要EDA工具的深度配合和創新突破。

四大技術趨勢成形 EDA產品創新勢在必行

面對這場3D封裝革命,台灣半導體產業需要在2025年下半年前完成關鍵佈局。因此產業界有三個方向需要重視:第一,加速培養熟悉先進封裝設計的EDA人才,預計需求將在未來兩年內增長300%;第二,支持本土EDA工具商在多物理域仿真領域的技術突破,這是打破國際壟斷的最佳切入點;第三,推動產學合作建立3D封裝設計的標準化流程,台灣有機會在這個新興領域制定遊戲規則。

當摩爾定律的傳統路徑逐漸走向終點,王誌宏認為透過2.5D、3D IC和先進封裝技術,讓半導體的發展可以延續某種頻率,這個曲線比較不會被傳統的技術瓶頸所侷限。更重要的是,系統級最佳化將成為未來競爭的關鍵,不僅只是晶片設計的系統,還考量晶片設計完之後,它放到PCB板上,PCB板上放到伺服器上,我們可以一路從晶片設計到整個系統,去做一個最完整的模擬驗證。

這種全方位的系統級思維,是未來半導體產業和EDA工具發展的核心方向。