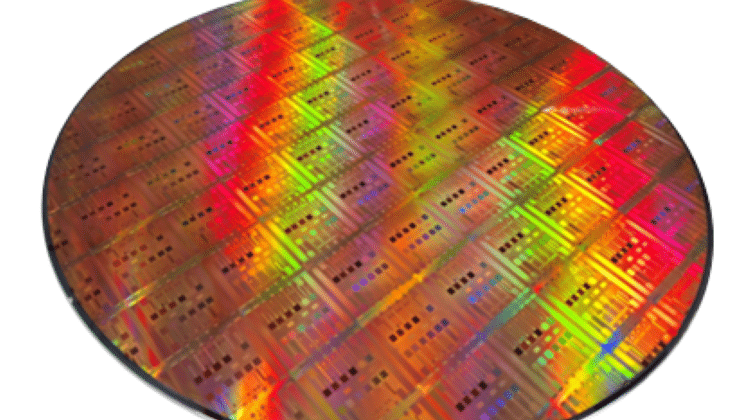

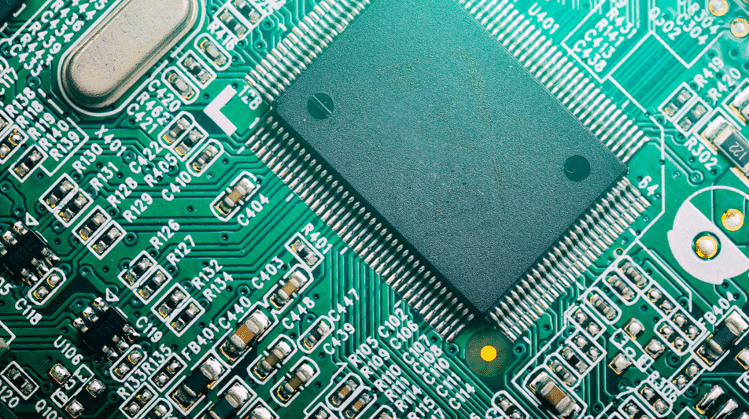

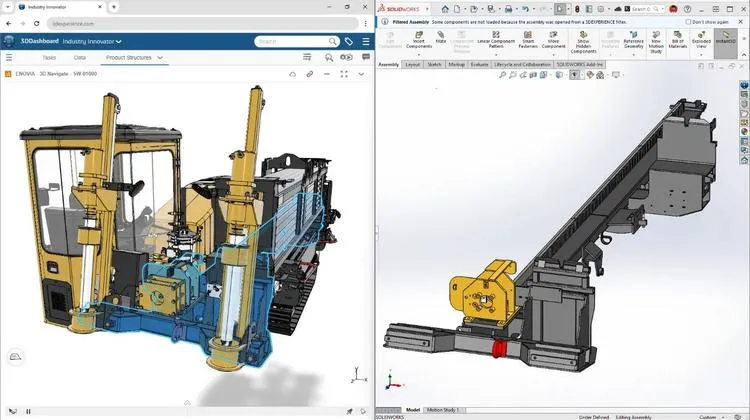

益華電腦宣布瑞昱半導體成功運用Cadence Encounter RTL Compiler具實體意識的RTL合成技術縮減數位電視SoC面積,並具體實現在高度整合的多媒體系統單晶片(SoC)–Imagination PowerVR SGX544MP2的40奈米(nm)設計上。

RTLCompiler獨特具實體意識的全面映射技術實現資料路徑最佳化,能夠縮小Imagination設計的關鍵元件。瑞昱半導體駕馭先進合成技術,更妥善地結構和映射邏輯到更小的網表(Netlist),並在量產運用EDI數位設計實現系統(Encounter Digital Implementation System)成功地收斂時序而獲得佳績。

瑞昱半導體發言人陳進興表示,由於切換至RTL Compiler讓該公司能夠實現縮減圖形處理器(GPU)設計的占用面積,而達成更快速的流程。瑞昱不斷努力提高瑞昱產品的價值,同時在給定的表現範圍內達到任何面積或功耗的縮減,能夠提供給我們的客戶在具競爭價格下更高效率的產品,就是脫穎而出的重要關鍵。

瑞昱半導體也同時在此複雜的40奈米GPU上首次採用Cadence的EDI系統於塊級(Block-level)的收斂,運用EDI系統的階層式設計方法(Hierarchical Flow)幫助實現更快的GPU和提升SoC設計定案(Tapeout)的可預期性。

益華電腦網址:www.cadence.com/tw