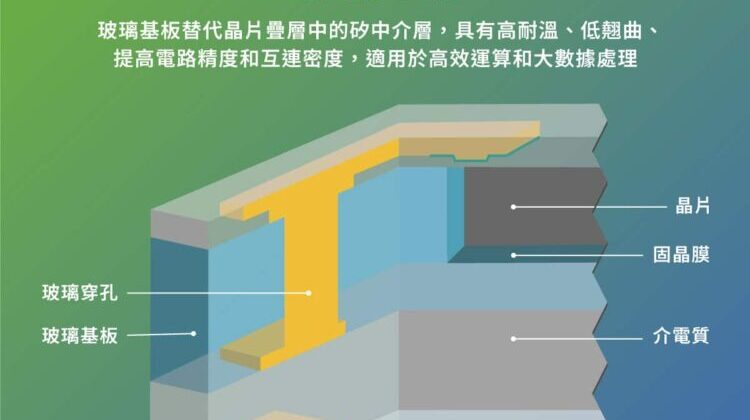

為延續摩爾定律(Moore’s Law),半導體製程微縮的技術創新方向不斷轉變。採用2D結構的互補式場效電晶體(CFET),將是下一個推動產業變革的技術。

引進較低性能的元件—imec採取的途徑

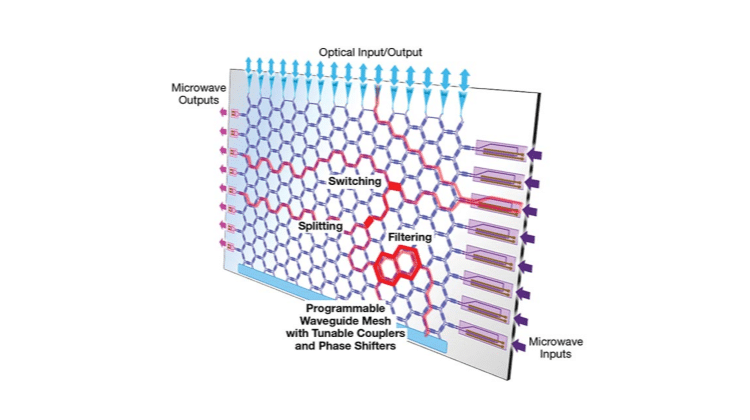

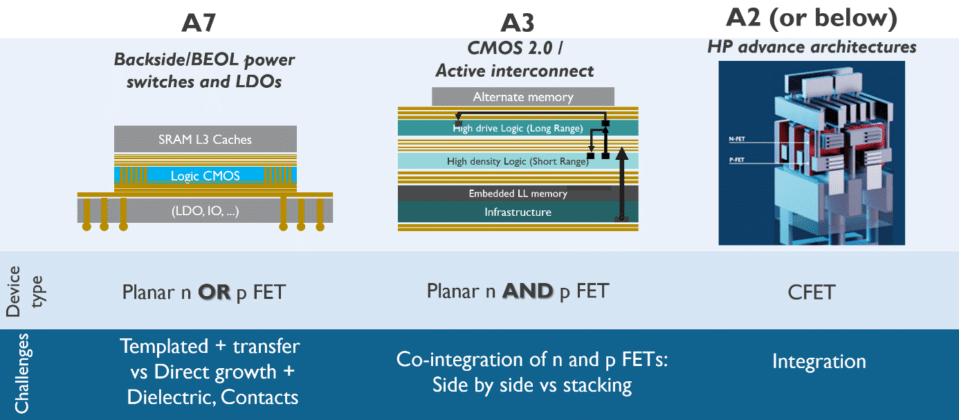

為了把2D材料引進最先進CFET架構的傳導通道,晶片大廠和大學團隊都正在探索解決方案。但imec選擇了其他方向,其背後推力是多項整合挑戰和預期成本的因素(圖3)。

為降低引進2D材料所需付出的心力和預期成本,imec選擇在較不先進的節點及較低性能的元件上逐步導入,著重在自家模組以及平面2D元件在12吋晶圓製程上的開發。把這些2D元件整合到高度複雜的CFET元件時,我們就能回顧這段期間的所學到的經驗。這些2D材料屆時也已經引進12吋晶圓廠,有關介電材料沉積和源極/汲極接點成形的解決方案也會就緒,而提升可靠度和變異性的不同發展路徑也會在探索的過程中。下文將詳解imec所採取的途徑。

0.7奈米技術節點的平面2D為基N型或P型FET

imec正在努力先將基於過渡金屬二硫族化物(MX2)的2D元件引進其邏輯技術發展藍圖的0.7奈米(A7)節點。在此新技術世代,包含矽通道的互補式場效電晶體(CFET)將成為高性能的邏輯CMOS,電源會透過晶背供電網路來布線到這些邏輯元件,而底層快取(LLC)記憶體也可能利用先進的3D整合技術來連接到邏輯CMOS。

基於過渡金屬二硫族化物的平面2D元件的發展契機在於周邊元件。這些元件可能是配置於BEoL製程,甚至是晶圓的背面。像是低壓差穩壓器(LDO),以及具備較低性能且用來啟動(及關閉)邏輯CMOS元件區塊的電源開關。

imec研究人員進行的模擬結果顯示,搭配過渡金屬二硫族化物通道的平面nMOS元件,在這類應用上極具潛力。晶圓背面或後段製程將有更多的可用空間來實作這些元件。因此,相較於位於晶圓正面的(昂貴)相應元件,這些平面元件的接點配置能更鬆弛,為更大型的平面元件架構預留空間,不論是N型或P型。

針對這些應用,元件層轉移是獲得青睞的沉積技術:BEoL製程和晶背處理流程為了不損害配置在晶圓正面的元件的性能,兩者皆把可用的溫度預算限縮在400°C以下。在這樣的低溫狀態下(運用業界相容的技術來)直接成長2D材料極具挑戰,因為這種作法可能會製出低品質的元件層。

0.3奈米節點的平面2D為基N型或P型FET

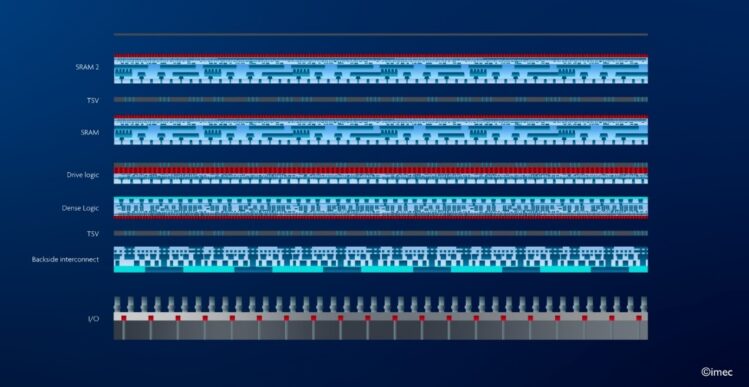

同時,把該材料導入imec 0.3奈米(A3)技術節點的開發工作也在進行中。對此,imec預期將會逐步轉換到CMOS 2.0—把異質整合帶入運算系統單晶片(SoC),進而釋放摩爾定律發展潛能的一次典範移轉。為了做到這點,方法是借助系統技術協同最佳化,把系統單晶片重新分為不同的功能層,並運用先進的3D內連和晶背技術來重新連接這些元件層(圖4)。

與其在SoC的各功能部件使用最先進的節點,這些功能層可以採用最接近各自性能限制的技術選項來製造。需要超高元件密度的元件層(例如密集型邏輯電路)會由最高度微縮的技術,亦即互補式場效電晶體組成。

CMOS 2.0能讓2D材料順利引進SoC內部的不同元件層。例如,電源開關用來當作晶背主動內連導線的部份,或者平面式過渡金屬二硫族化物元件作為記憶體層的部分。

以2D材料為基礎的GAA奈米片和CFET

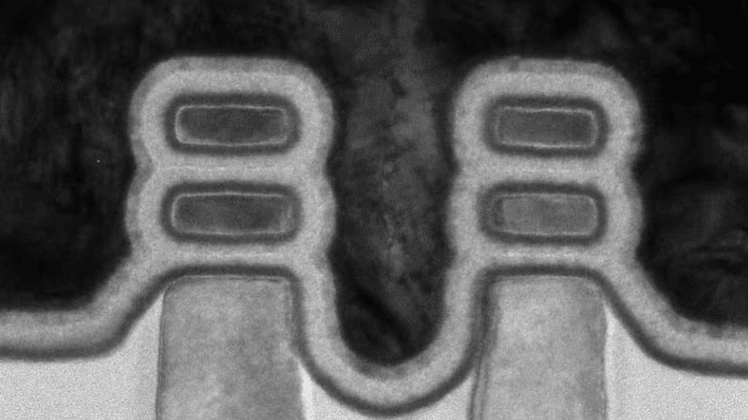

雖然上述研發都在12吋晶圓無塵室內進行,但imec同時也在探索引進2D材料來作為環繞閘極(GAA)奈米片電晶體的傳導通道。這些研究在研究室的規模下進行,不過確實採用與晶圓廠相容的工具和製程。這些調查的目標是探究2D材料整合對奈米片專用模組的影響,更長期來看,這些模組將與CFET有關。想想看奈米片通道的推出(亦即移除犧牲層,以形成奈米片通道)、內襯層的成形,以及替代金屬閘極的整合步驟。

在低性能平面過渡金屬二硫族化物FET學到三堂課

透過在低性能平面過渡金屬二硫族化物FET上所累積的經驗,我們可以得到三種在12吋晶圓先進製程上不可或缺的能力,分別是元件層轉移、pFET整合以及更高的可靠度。

邁向均勻和高品質2D單原子層的可行道路

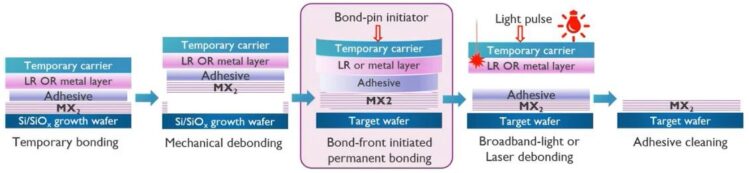

2D材料的模板化材料成長與元件層轉移,是在400°C以下於12吋目標晶圓沉積高品質2D材料層的有趣方法。藉由模板化的材料成長,單片預定義的「模板」基板(例如藍寶石)用來控制2D材料的成長,使其長出單一晶體方向。接著,橫跨整片12吋晶圓表面的超薄材料層必須在未斷裂的情況下轉移到目標晶圓。

於2024年IEEE國際超大型積體電路技術研討會(VLSI Symposium),imec展示了一套12吋晶圓過渡金屬二硫族化物乾式轉移製程(圖5),結果首度實現可重複在整片晶圓上達到絕佳均勻度(材料型態產量高於99.5%)的製程。另外,缺陷數量也比其他的元件層轉移方法還要低了許多。

取得這些突破性成果的關鍵是在高性能的接合階段運用鍵合波的起始反應,並在釋放臨時載板時採用晶圓光子剝離技術。鍵合波起始反應的基礎是先在晶圓中間施加鍵結力,接著該鍵合力朝向邊緣傳遞。這些技巧顯示了可以緩解孔洞的形成、改善接合的均勻度,以及產生微量甚至毫無殘留物。

這使得元件層轉移成為2D材料沉積應用的可行技術選項。此次提出的製程運用晶片產業熟知的(在3D系統單晶片和小晶片整合的發展環境下)12吋晶圓相容製程步驟。

在GAA奈米片進行元件層轉移並取得良好的一致性與品質

這支imec研究團隊已經把他們在平面元件進行元件層轉移時所獲得的知識應用到環繞閘極(GAA)奈米片的測試元件。其研究結果顯示基於實驗室的過渡金屬二硫族化物nFET具備傑出的一致性、均勻性和材料層品質。元件層轉移是用來形成奈米片通道(所以也用於CFET)的矚目方法,偏好在溫度600°C以下運作。

或者imec探索在更低溫的狀態下直接成長2D材料,但這種做法只有在沉積尺寸較小的選定區域,才能製出高品質的元件層。

鎖定基於2D平面pFET的12吋晶圓整合平台

到目前為止,多數的整合研究都在N型元件上進行。2023年IEEE國際電子會議(IEDM)上,imec攜手英特爾首次展示12吋整合式平面二硒化鎢pFET電晶體,採用的是一套類似用於二硫化鉬(MoS2) nFET製程。這些團隊也詳細分析了晶粒大小對該元件性能與可靠度的影響。

強化可靠度與變異性的發展道路

在量化基於2D材料的元件可靠度與變異性方面,imec與維也納理工大學(Tibor Grasser教授的研究團隊)在前幾年取得了進展。舉例來說,他們研究了2D材料層厚度、晶粒大小和方向以及2D成長模板對12吋整合式過渡金屬二硫族化物平面元件性能的影響。他們也能指出造成可靠度和變異性問題的根本原因,目前也在努力找出研究方案。

共同合作面對未解挑戰

儘管世界各地的多個研究團隊已經取得重大進展,但仍需一些技術突破來消弭邁向先進節點量產的技術差距。imec認為,與晶圓廠相容的源極/汲極接點成形、可控制摻雜與實現包含過渡金屬二硫族化物元件的CMOS(即整合P型與N型FET)是最關鍵的未來挑戰。解決這些問題需要共同合作,包含業界領導者、大學團隊和研究機構,以及工具開發商。

解決了這些問題,2D材料的未來將會一片光明。這些材料不只可望推進0.7奈米(A7)之後的邏輯微縮發展,其材料特性還能拓展遠超過邏輯元件以外的應用領域。2D材料在關閉狀態下具備極低電流的優勢,所以在嵌入式動態隨機存取記憶體(DRAM)應用展現了發展潛能—有望從0.7奈米(A7)節點開始導入。此外,「類表面」2D材料的傳輸性質非常容易擾動,這也使得這些材料非常適合用於機率運算或甚至是機器學習(ML)應用。

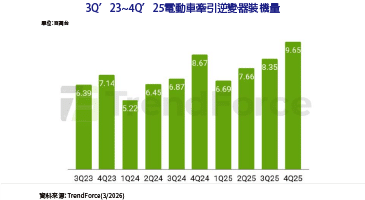

從2D FET到2D CFET 製程微縮帶動2D材料需求(1)

從2D FET到2D CFET 製程微縮帶動2D材料需求(2)