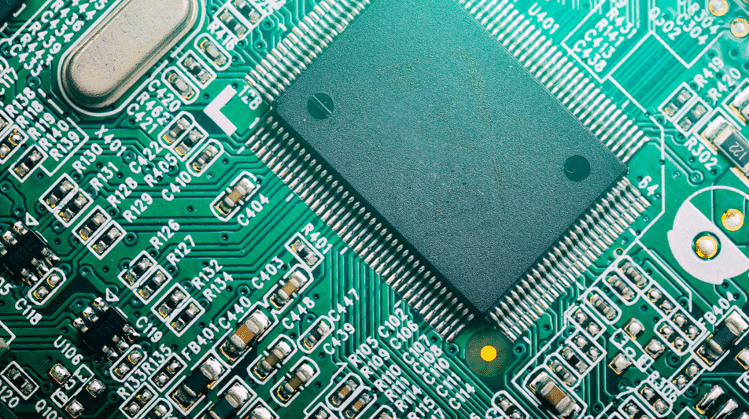

茂綸推出ASIC Prototyping Board,其為採用Altera Stratix II系列Fine-Line BGA 1508 Pin包裝的FPGA,最大可提供將近十八萬個邏輯單元、9,383K RAM Bits、九十六個36×36硬體乘法器及十二個整合式鎖相迴路(PLL),在10公分×12公分基板面積下可提供最大一千一百個輸出入接腳,所有I/O接腳透過四個高速高密度的Samtec連接器與主板連結,由於目前高容量的FPGA在加工製程及測試都需花較多的時間來完成,如何快速有效的完成一個ASIC平台,提供ASIC硬體軟體設計人員在此平台無誤的完成設計驗證及偵錯,此款ASIC Prototyping Board是一個解決問題的途徑,對於ASIC Prototyping System的製作提供最佳的彈性及快速可靠的方法。

使用大容量FPGA元件來作ASIC設計的驗證平台,已是普遍的做法,不僅可快速的確認ASIC邏輯設計是否正確外,也可在設計早期作有限度的確認ASIC功能在真正的應用中是否符合所需,一般而言,大型的ASIC設計在驗證上主要的需求以FPGA容量的大小及輸出入接腳的多寡為主,FPGA的容量大可讓ASIC在設計時不須為了FPGA容量過小而作切割,輸出入接腳越多則可提供越多訊號輸出以作為電路除錯(Debug)的方便訊號監測。

茂綸網址:www.gfec.com.tw

登出中,將自動重新整理頁面

熱門關鍵字: