賽普拉斯(Cypress)與Hi-Tech發表編譯器技術,能有效擴充可動態調整的PSoC混合訊號陣列中的記憶體容量與效能。此新款符合ANSI規範的C語言編譯器–專為PSoC混合訊號陣列量身設計的Hi-Tech C PRO,運用Hi-Tech的全知程式碼產生技術(Omniscient Code Generation, OCG),可大幅縮減PSoC程式碼大小。

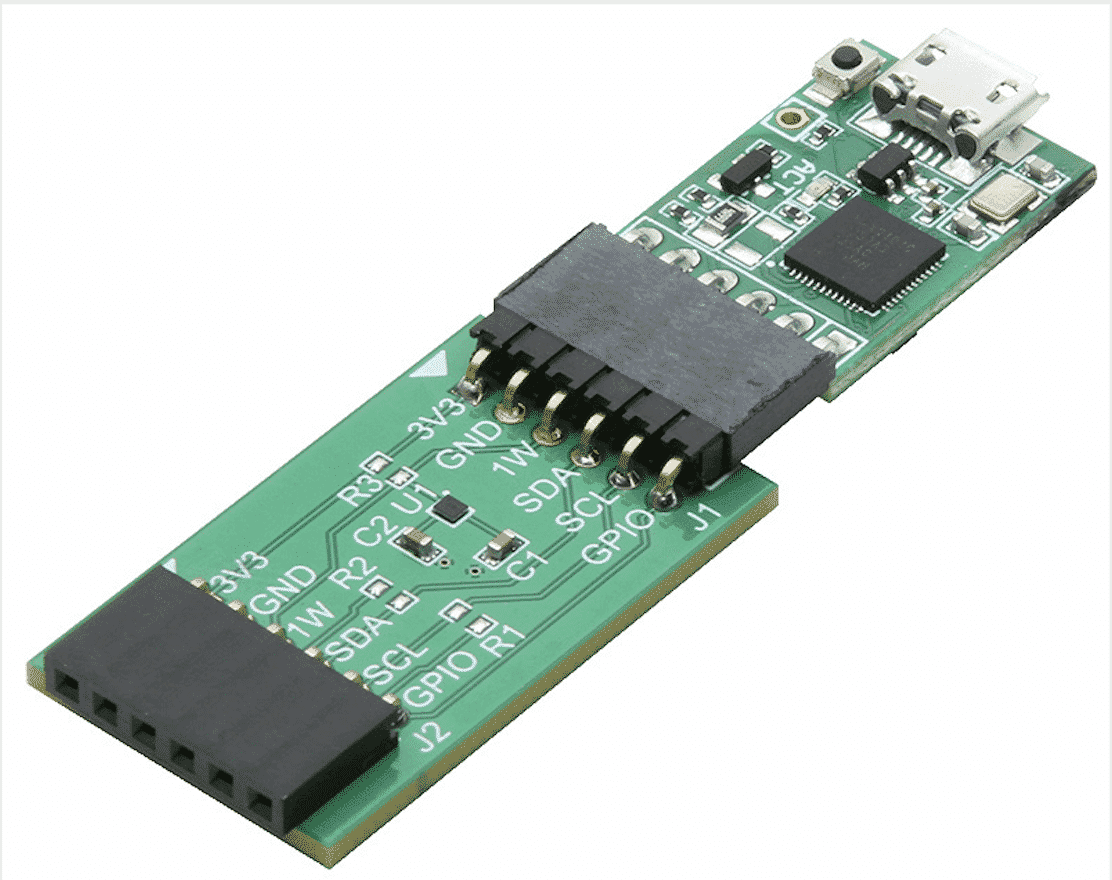

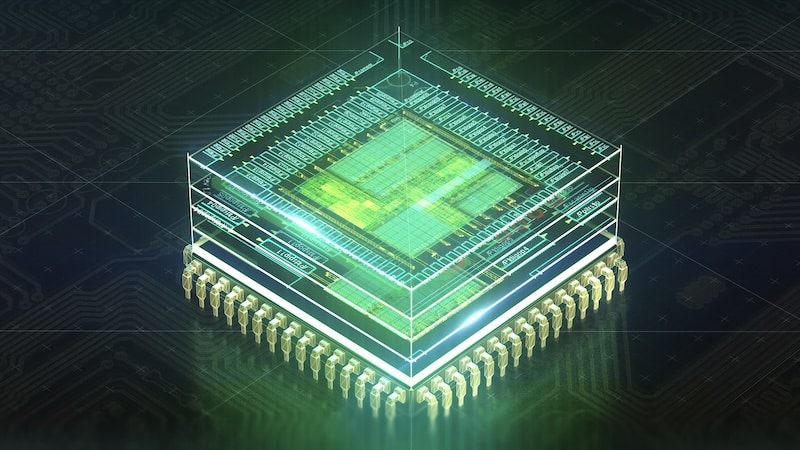

PSoC混合訊號陣列將可編程的類比與數位功能與8位元MCU核心整合在一起,並包含最大可達32Kbyte的快閃記憶體及最大可達2Kbyte的SRAM。PSoC混合訊號陣列可廣泛運用在各種注重成本及有空間限制的消費性應用,包括觸控螢幕介面、馬達控制及近距離偵測等。PSoC元件具備動態調整功能,並可由同一個矽元件執行多個獨立運作的功能,因此能降低元件數量、機板空間及電源消耗。

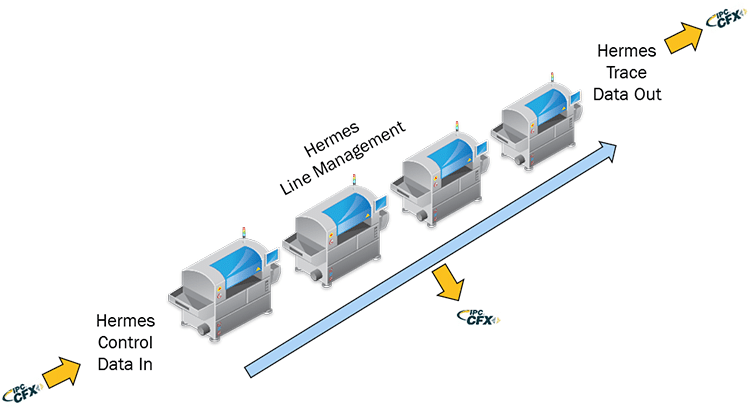

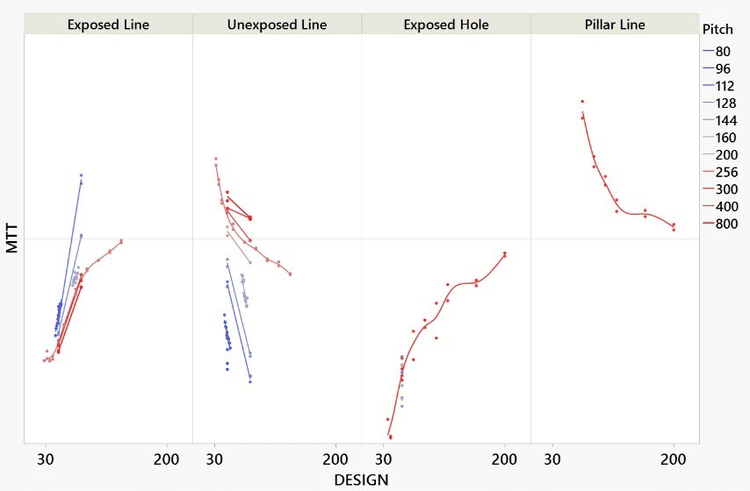

鎖定PSoC混合訊號陣列的Hi-Tech C PRO編譯器採用OCG技術,在檢查所有程式模組後,再進行編譯與指標、暫存器和堆疊配置的最佳化及刪除多餘程式碼等作業。編譯器能釋放出SRAM空間,並針對所有非遞迴與非重進入的程式碼,編譯直接定址與最佳化函數堆疊,以減少PSoC元件索引暫存器競用資源的狀況。由於縮小的程式碼能在更少的週期內執行完畢,因此,新款編譯器亦可增加PSoC元件的效能。

賽普拉斯網址:www.cypress.com

-e1762940635172.jpg)