工業、汽車、伺服器、電信和資料通訊應用都需要先進的系統單晶片、現場可程式化邏輯閘陣列(Field Programmable Gate Array, FPGA)和微處理器解決方案。這些解決方案需要多個低壓電源,包括用於DDR的1.1V、用於核心的0.8V,以及用於I/O裝置的3.3V/1.8V。隨著半導體整合度不斷提高,微處理器的耗電量越來越大,因此需要更大的供電電流。

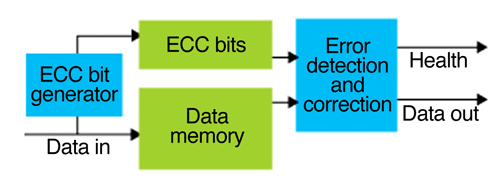

同時,市場亦對採用FPGA或微處理器的電源監控技術表現出強勁需求。此類技術能夠監測電壓、電流、溫度和其他裝置參數。為了簡化設計方案,可透過整合I2C/PMBus的模擬電源IC來監測這些關鍵參數並進行電源管理與監控。

因此,電源解決方案必須與I2C/PMBus整合,以支援電源監控回讀和穩壓器可程式化設定,同時實現更大電流能力、更高效率和卓越的抗電磁干擾(Electromagnetic Interference, EMI)性能。擁有高性能且滿足這些要求的多相元件正變得越來越受青睞。本文將介紹一款雙相降壓型穩壓器的一些設計思路。此款穩壓器的兩個通道可以提供兩相合計高達40A的連續電流,單一通道最高支援可達30A。其整合了數位電源系統管理功能,可支援透過符合PMBus/I2C標準的序列介面進行編程和電源監控。設計時則須審慎考量,以達成尺寸、效率、迴路穩定性和瞬態響應等方面的目標。

提升效率關鍵

假設一個應用需要從12V電源獲得1V、30A的低電壓、大電流輸出,且效率為80%,則總損耗將達到7.5W。這些損耗會變成熱量,導致IC和電感的溫度上升。資料中心的環境溫度通常高於室溫,額外的損耗會使IC的溫度進一步升高,進而更接近IC的熱關斷限值(通常為150°C)。對於負載點(Point of Load, POL)電源應用,此類問題尤為關鍵,因為DC-DC轉換器往往非常靠近高發熱量的微處理器。

下文將說明幾種有助於提高低電壓、大電流元件效率的方法。

SW節點PCB布線要點

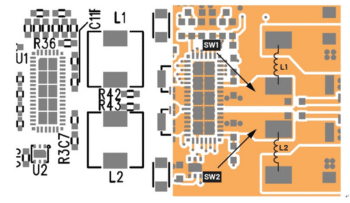

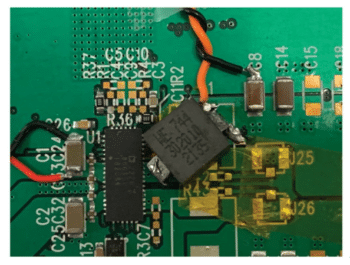

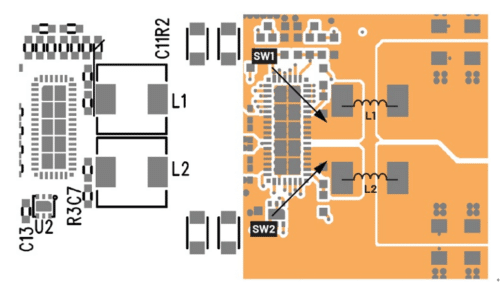

在之前版本的雙相元件展示板設計中,第1相和第2相中的電感相對而置,如圖1所示。如果電感以此特定方向放置,EMI性能會更好,但缺點是開關(SW)節點的布線較長,尤其是在重負載條件下,因導通損耗與電流值的平方成正比(P=I2R),將導致PCB布線損耗增加。

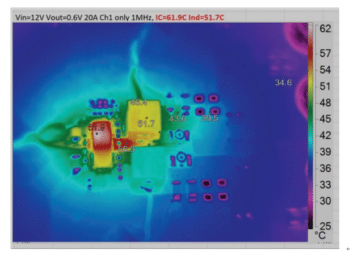

圖2所示為20A負載條件下的熱像圖。開關節點溫度極高,幾乎與IC相同,但只要調整設計就可以改善PCB布線引起的損耗。

圖3的測試設定中,對PCB進行了切割處理,並移動通道1電感,使之更靠近IC,以縮短SW節點布線。

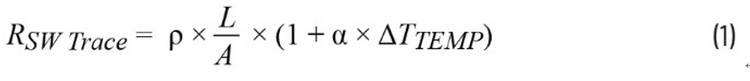

根據PCB布線的銅厚度和長度,SW節點的直流電阻為:

其中:

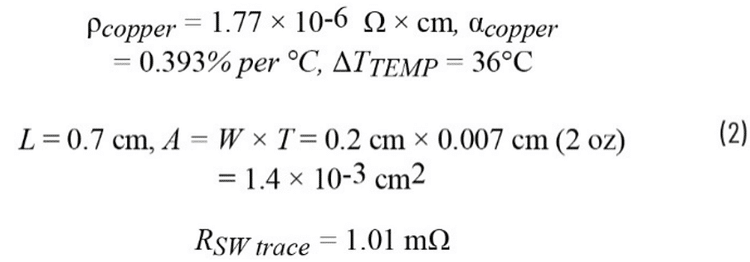

總損耗為:

其中:

在20A負載條件下,SW節點產生的預期損耗為:

將SW布線縮短L=0.3cm後,損耗改善為:

計算得出的預期損耗改善幅度為:

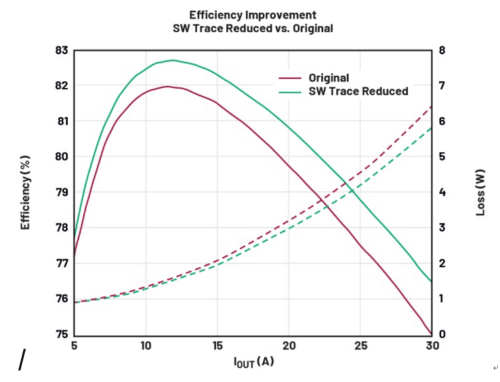

圖4顯示了測試結果的效率改進情況。在20A和30A負載條件下,損耗改善幅度分別為0.22W和0.53W。

當負載提高時,效率差異會更大,表示此PCB布線的導通損耗(P=I2R)將占主導地位。在滿負載條件下,效率可提升1.5%。由於電感無法太靠近IC,因此在第二版的電路板布局中,電感會旋轉90°面向IC,以縮短SW布線長度,如圖5所示。

加強輸入電容降低振鈴

研究過程中發現,輸入電容對低電壓和大電流應用的效率與穩定性也有重大影響。工程師常忽視輸入電容設計的重要性,憑藉過往經驗來布置輸入電容。然而受到PCB方案總尺寸限制,工程師布置的輸入電容不足,可能導致電路不穩定並產生更多損耗。

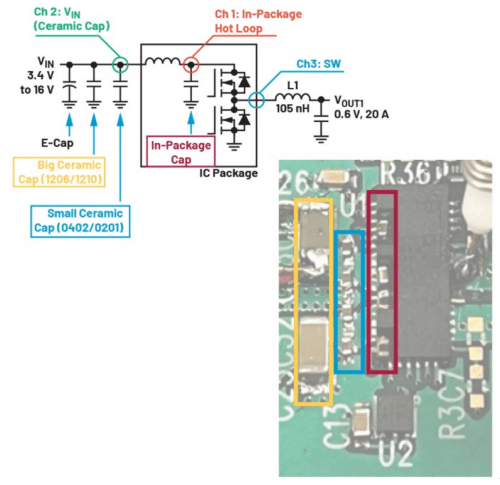

圖6從左到右分別顯示了用於熱插拔和抑制突破電流的電解電容,大陶瓷電容(通常為1210或1206尺寸)用於減少輸入電流漣波,而小陶瓷電容(0402或0201尺寸)則用於減少高頻漣波。除此之外,Silent Switcher2技術會將一對電容嵌入封裝中,以減少SW高頻雜訊和過沖。圖6右側下方的圖片顯示了兩個1206陶瓷電容(黃色)、四個0402封裝外陶瓷電容(藍色),外加四個採用去封裝技術的0402封裝內電容(紅色)。封裝中晶片上方刻蝕一個孔,以露出襯底上的封裝內電容。

使用探頭對這些輸入電容和開關節點進行探測,觀察不同輸入電容組合的過程。

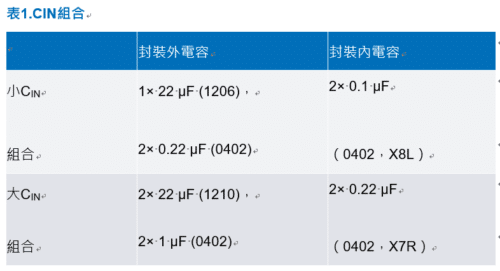

然而,這導致了IC的最高工作溫度範圍從150°C(X8L)降低到125°C(X7R)。有時候,IC的最高溫度是一個重要考慮因素,因為部份應用如資料中心等,其工作環境溫度極高,常常超過70°C。如果選擇X7R封裝內電容,工程師需要注意其最高溫度可能會超過工作範圍。

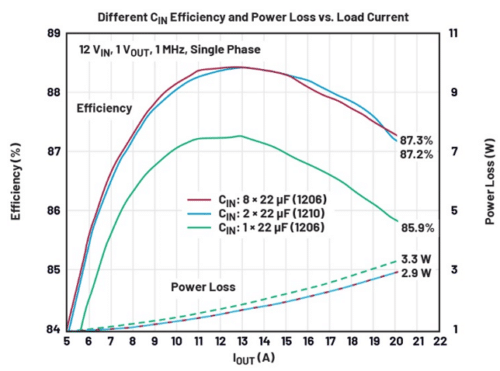

更高的輸入電容(Inrush Current, CIN)不僅能提升開關的穩定性,還有助於提升效率。圖7顯示,如果增加足夠的輸入電容,效率將提高約1.4%,損耗降低0.3W。輸入端的振鈴和壓降會導致開關損耗增加。8個1206尺寸的電容與2個1210尺寸的電容具有相似的效率,因此在這種情況下,理想的CIN選擇將是2個22μF的1210尺寸電容。

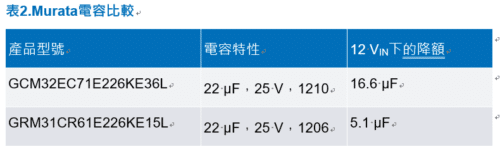

對於輸入電容的選擇,由於陶瓷電容具有較大的直流額定範圍,因此工程師還應注意直流降額。例如,比較12V下1206和1210電容的直流降額,1206尺寸電容的降額更為嚴重。表2列出了兩個Murata電容作為示例。有鑑於此,建議使用1210尺寸電容作為低電壓、大電流電源的輸入。

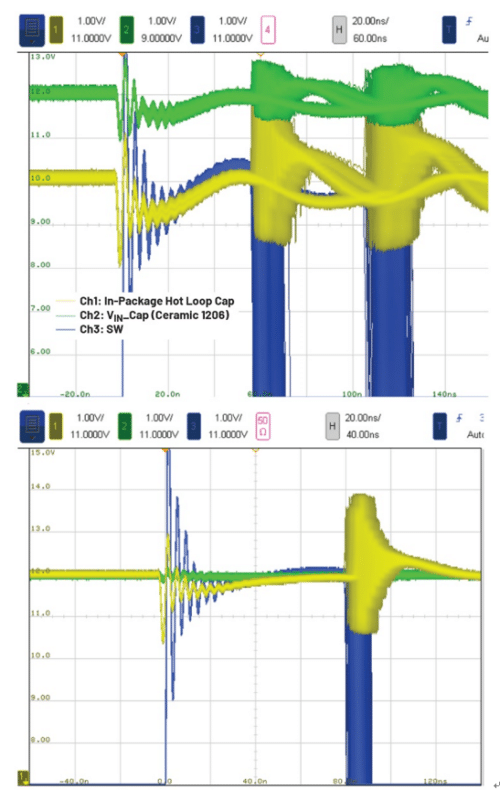

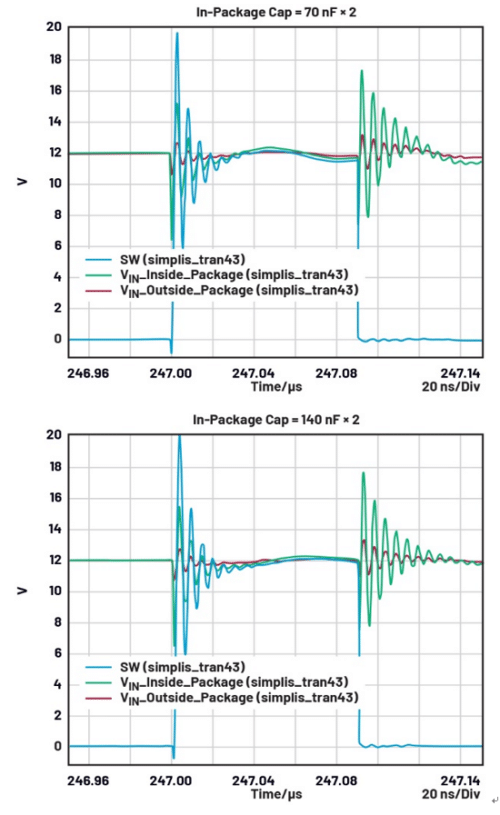

如果總輸入電容較小,如圖8上方波形,在重負載條件下,SW節點波形會出現較大的振鈴。這是因為當頂部開關導通時,大部分電流將是從輸入電容中拉出。總電荷量=電容×電壓(Q=CV)。因此,如果電容較小,CIN將會有較大的壓降。CIN與輸入布線和IC封裝的寄生電感將形成LC諧振電路,導致開關節點處出現振鈴。大電壓降也會導致SW失真和不穩定,在小脈衝後面跟隨一個大脈衝。

增加輸入電容以抑制振鈴,可以改善開關的不穩定性。相較於小CIN組合,大CIN組合的總電容值翻倍。CIN越接近開關的頂部,改善幅度就越大,故建議可增加封裝內電容的值。在以往案例中,兩個0.1μF(0402、X8L)電容增加到0.22μF(0402、X7R)(見表1)後,開關變得穩定,如圖8的下方波形。

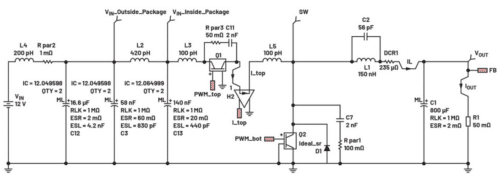

SIMPLIS模擬是一個有用的工具,可協助工程師確定CIN的最優值。圖9顯示一個降壓型穩壓器,並標出了沿著電源布線的寄生電感估計值。輸入電容已根據12V輸入電壓下陶瓷電容的直流降額進行了調整。如果輸入電容翻倍,從2x70nF增加到2x140nF,振鈴會得到改善,如圖10所示。

本文重點在於低電壓、大電流的電源設計,並介紹兩種方法來提高重負載條件下的效率。根據PCB上開關節點的熱點(其溫升幾乎與IC相同),可採取改變電感方向、縮短開關節點布線長度等方式來降低損耗。輸入電容的設計極為重要,但也常被忽視。輸入電容不足將導致電源不穩定且效率低下。在低電壓、大電流電源的設計中,應用工程師需要特別注意輸入電容的平衡。

(本文作者為ADI資深應用工程師)