ARM日前宣布推出一款與NEC Electronics攜手研發的新型態MPCore處理器。MPCore可合成多重處理器是以ARMv6架構為開發基礎,可建構成最多至4顆處理器的組態,並提供2600 Dhrystone MIPS效能。此外,MPCore多處理器亦具有Adaptive Shutdown及ARM Intelligent Energy Manager技術,可有效降低85%耗電率。NEC Electronics 將運用此新款ARM處理器開發消費性電子、汽車及行動裝置等產品。

新款ARM多重處理器解決方案能以低於其它單一處理器解決方案的時脈頻率達到更高的效能,並藉此協助系統研發業者大幅降低成本。此外,多重處理器亦能滿足各種高效能需求的應用,使得家用與車上型消費性娛樂及匯整型裝置(convergence devices)等此類產品可同時執行多項工作。例如當使用者透過網際網路分享家庭電影時,視訊轉換器依然能同時錄下多個電視頻道的節目;而車用導航系統則能同時提供即時後座電視遊樂器的功能。

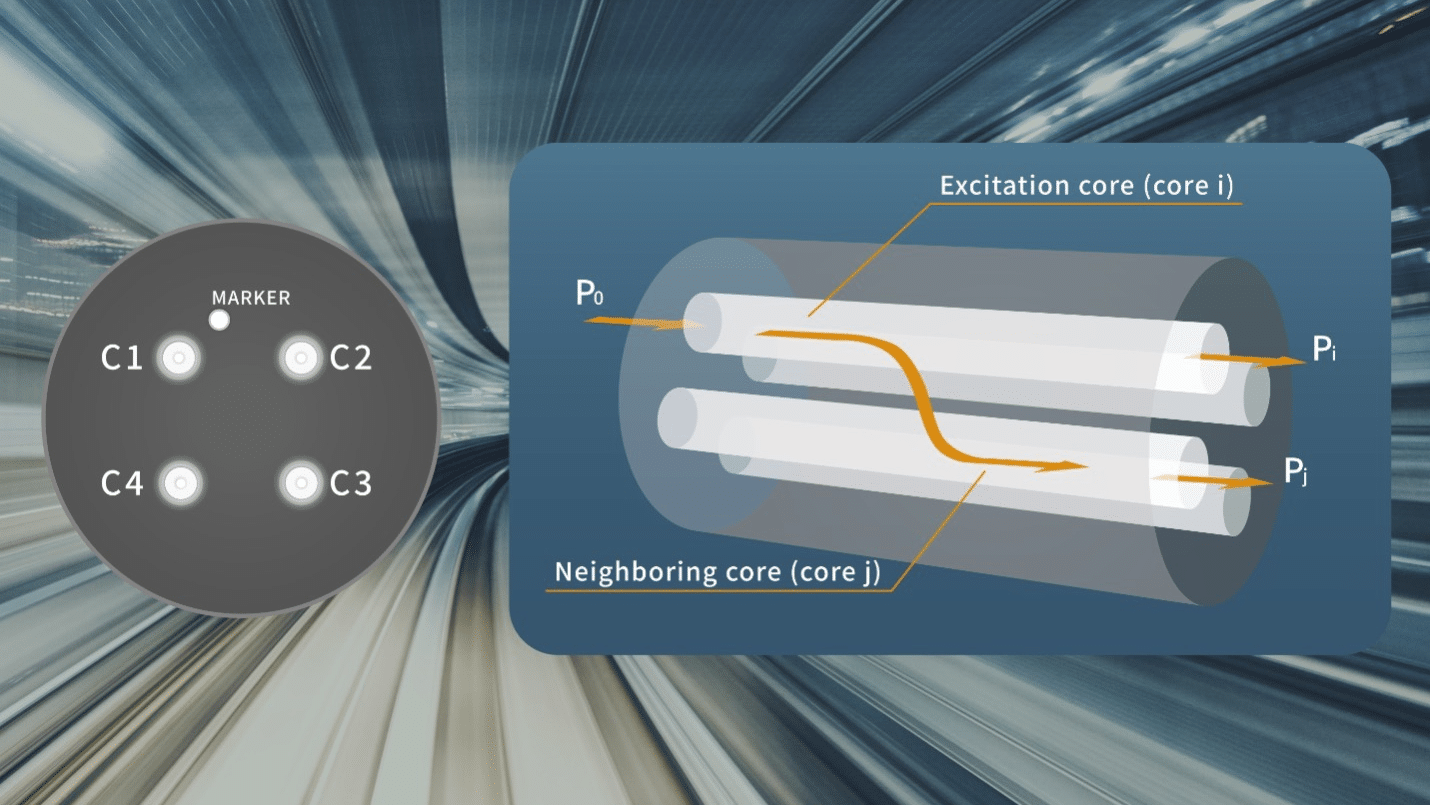

MPCore支援多達4路快取的協同式對稱多工處理(four-way cache coherent symmetric multiprocessing, SMP)、多達四路的非對稱多工(four-way asymmetric multiprocessing, AMP),或混合以上兩種模式。此種彈性化的設計能提高流量及系統處理的反應速度,使現有的應用具備可移植性,並提升多緒(multithreaded)應用可擴充的軟體效能。這種支援多工作業的能力可協助各種網路裝置處理更高的封包流量及更高的資料處理量。

MPCore支援ARMv6架構,搭配SIMD媒體延伸指令以支援新一代多媒體與匯整型裝置並發揮ARM Jazelle Java軟體加速的效能。MPCore支援一至四顆處理器的組態,並使用修訂版MESI協定以建立快取的協同機制。它亦搭載可調整的第一階快取記憶體、64位元的AMBA AXI介面、向量浮點運算的協同處理器以及可編程的中斷機制。處理器支援Adaptive Shutdown技術,能適時關閉沒有使用的處理器,不包括快取記憶體,其所需耗電率僅57mW/MHz,並擷取原生型130奈米製程技術。ARM Intelligent Energy Manager技術能機動地預測所需的效以進一步降低耗電率,並降低電壓與時脈頻率。MPCore使系統研發業者將核心視為單一的整合型處理器,故能簡化研發作業並縮短產品上市時程。

ARM現已開始提供MPCore多處理器的授權方案,首款矽元件產品可望在2005年第2季問市。MPCore多處理器的評估系統所搭配的Linux 2.6作業系統與相關研發工具現已開始供應,使業者能提早針對MPCore多處理器所研發之產品開發支援軟體。