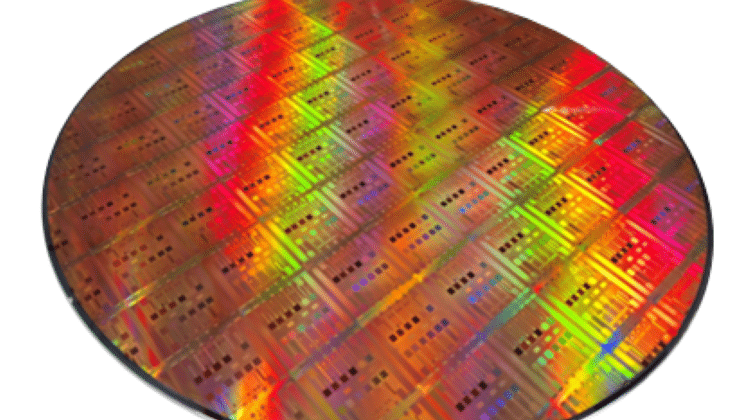

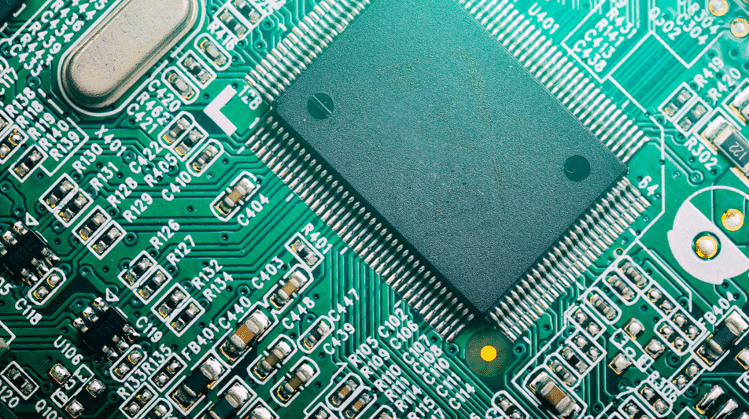

創意電子(GUC)宣布其在台積電16奈米(nm)FinFET Plus(16FF+)製程上採用益華電腦Encounter數位設計實現系統完成高速運算特殊應用積體電路(ASIC)的設計方案。

創意電子總經理賴俊豪表示,創意電子身為ASIC設計的先鋒,必須能及時將非常複雜的設計提交給客戶,益華的工具和團隊在這方面給予了極大的支持。在完成這第一個16FF+產品流片之前,創意電子採用益華的工具實現幾次16納米的測試晶片的流片,都獲得非常好的晶片測試結果。

創意電子運用Cadence Encounter數位設計實現方案解決在16FF+上出現的設計挑戰,包括增加的雙重成像和FinFET設計規則檢驗(DRC)、時序和功耗變化以及處理量的要求。

此外,該公司還結合16FF+制程的性能優勢,並採用益華的設計解決方案可以使ASIC操作時序提升18%,且功耗減少28%,系統性能提升兩倍。

Encounter系統還具備正確的架構、完整的雙重成像和涵蓋平面規劃、配置,以及電子和物理簽收的路徑的FinFET流程,且和Litho物理分析儀及CMP預報器的無縫整合,組成可製造設計(Design-for-Manufacturing, DFM)。

創意電子網址:www.globalunichip.com