資料中心市場若要採納400G Ethernet(400GbE)主要將面臨三大挑戰:更低成本、更低耗電以及採用更高速的SerDes,這三者之間也將彼此相互影響。

資料中心不停的追求更高的效能,促使業界發展出更快的介面速度。賽靈思(Xilinx)有線IP行銷部門經理Amy Chang指出,SerDes的高速序列介面是促成介面技術快速進展的關鍵技術,目前使用的SerDes技術為32GT/s。賽靈思以及少數幾家供應商現在能透過三公尺以上的銅導線與光纖支援56 GT/s的傳輸速度。

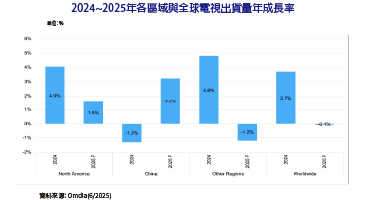

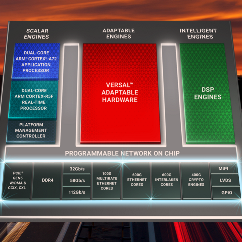

在未來三至五年,SerDes技術的鏈路速度將翻倍至112GT/s,而賽靈思未來推出的Versal系列產品也將皆支援此速度。目前業界主流的SerDes世代支援25G NRZ,並需要16鏈路的25G通道來支援400GbE乙太網路解決方案。隨著業界開始廣泛採納56G PAM4收發器,400GbE技術的成本與耗電需求將逐漸下滑,而112G PAM4在幾年內也會跟進。

賽靈思採用16×25G的介面及軟體矽閘極(Soft Silicon Gates)技術來展示400GbE方案的半導體廠商。賽靈思近期已開始出貨新款可支援8×53G 400GbE IP的UltraScale+ 58G系列元件,而預計在2020年將隨後推出112G。

Chang進一步說明,由於各界需要更高的資料傳輸率,FlexE將透過現有的低成本實體層,承載這些更高的資料傳輸率。賽靈思已採用標準型低成本100GbE技術,在4x100GbE FlexE上達到400GbE的傳輸率。在未來,該公司目標是透過N×400bG實體層運行更高的資料傳輸率(Terabit等級)。賽靈思將採用低成本的技術,來提供軟體IP促成這些更高的資料傳輸率。