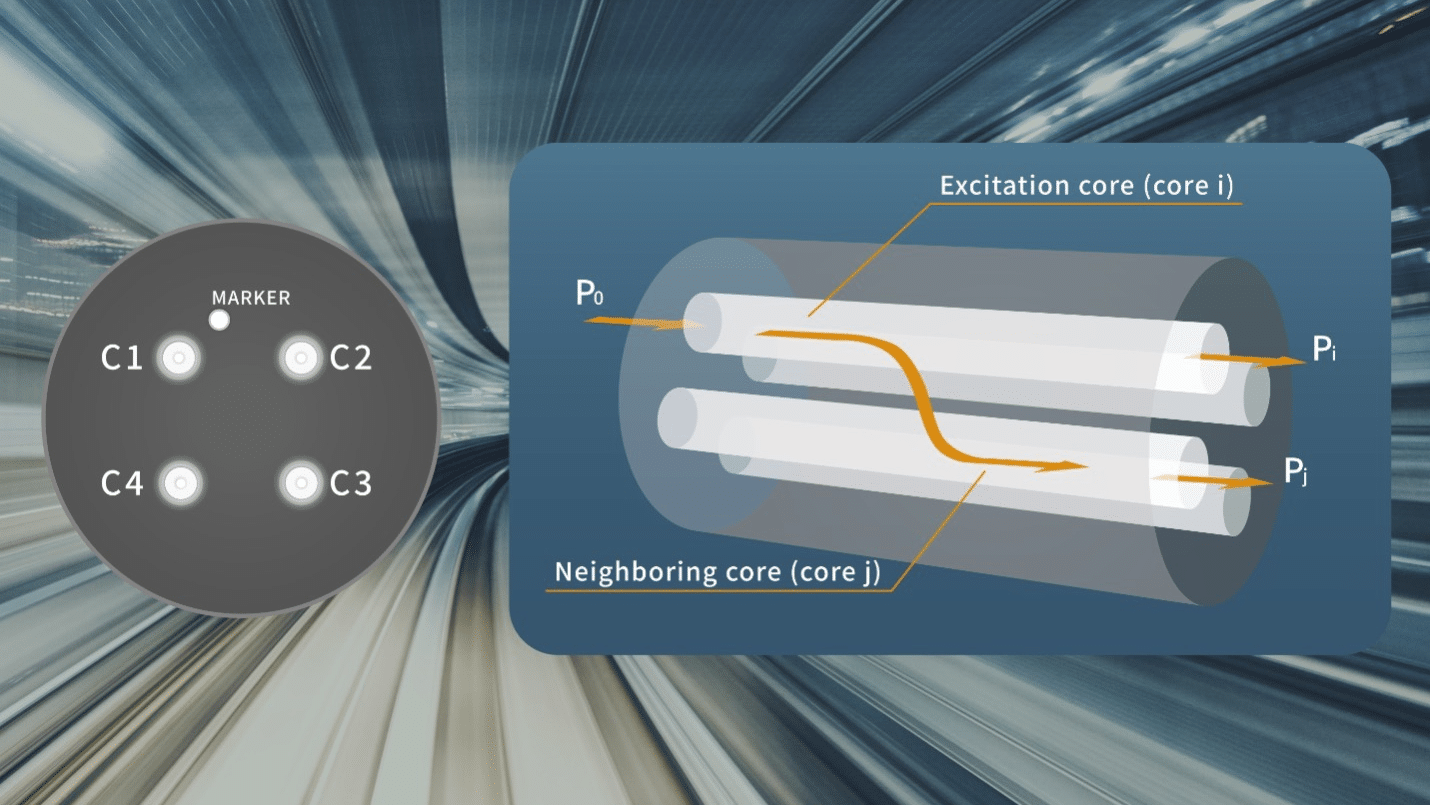

意法半導體(ST)宣布格羅方德(GLOBALFOUNDRIES)將採用意法半導體獨有的完全空乏型矽絕緣層金氧半電晶體元件(Fully Depleted Silicon-on-Insulator, FD-SOI)技術,為意法半導體生產28奈米和20奈米晶片。

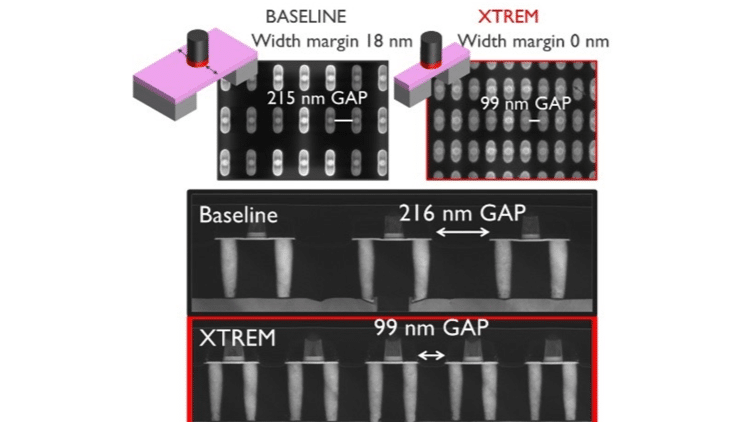

意法半導體負責設計支援和服務的企業副總裁Philippe Magarshack表示,因為沒有MOS歷史效應影響(MOS-History-Effect),從28奈米傳統互補金屬氧化物半導體(CMOS)製程(Bulk CMOS)技術向28奈米FD-SOI移植軟體庫和物理IP內核很簡單,使用傳統的CAD工具和方法研發FD-SOI數位系統單晶片與研發傳統CMOS製程技術完全相同。

Magarshack進一步指出,透過動態最佳化電路基片(俗稱襯底),FD-SOI還可讓同一晶片具有極高性能或極低功耗,FD-SO在低電壓條件下擁有出色的性能表現,能效明顯高於傳統CMOS製程技術。

憑藉其注重成本效益的平面型FD-SOI技術,意法半導體推出28奈米的完全空乏型元件。為提供FD-SOI貨源雙重保障,意法半導體與格羅方德簽訂代工協定,以補充意法半導體位於法國Crolles工廠的產能。

與此同時,28奈米FD-SOI元件目前已商用化,預計於2012年7月前投入原型設計;而20奈米FD-SOI元件目前處於研發階段,預計於2013年第三季投入原型設計。

此外,意法半導體的FD-SOI技術已被ST-Ericsson用於下一代行動平台,這項技術將讓ST-Ericsson的NovaThor平台具有更高的性能和更低的功耗,在發揮最高性能的同時降低功耗達35%。意法半導體計畫對格羅方德的其他客戶開放FD-SOI技術,讓他們能採用28奈米和20奈米技術研發產品。

意法半導體網址:www.st.com