第二代Wide I/O(Wide I/O 2)標準千呼萬喚始出來。聯合電子裝置工程協會(JEDEC)轄下的固態技術協會(Solid State Technology Association)日前正式發布Wide I/O 2標準–JESD229-2。相較於第一代規格,Wide I/O 2介面的傳輸速率將顯著攀升,同時保留Wide I/O矽穿孔(TSV)架構的垂直堆疊封裝優勢,有助打造兼具出色速度、容量與功率特性的行動記憶體,滿足智慧型手機、平板電腦、掌上型遊戲機等行動裝置的需求。

JEDEC低功耗記憶體JC-42.6小組委員會主席Hung Vuong指出,Wide I/O 2行動動態隨機存取記憶體(DRAM)介面是一項突破性的技術,也是在2012年發布的Wide I/O標準之延伸。

事實上,除了Wide I/O 2介面之外,JEDEC在 8月下旬亦發布第四代低功耗雙倍資料率(LPDDR4)記憶體標準。Vuong進一步表示,隨著這兩項標準相繼問世,JEDEC為開發者提供一系列的行動記憶體解決方案,從而實現最大的靈活性;水平架構的記憶體設計可選擇LPDDR4標準,垂直架構則有Wide I/O 2介面支援;而無論是哪種解決方案,都能提供符合現今市場需求的記憶體效能。

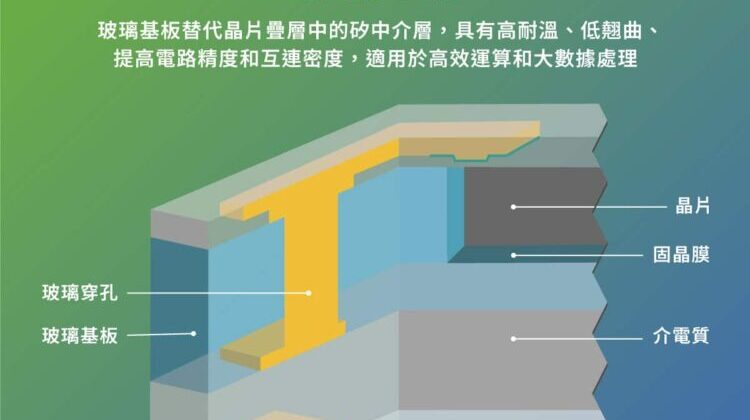

據了解,與第一代Wide I/O規格相比,Wide I/O 2提供四倍的記憶體頻寬(68GB/s),在1.1伏特(V)電壓供應下,有更低的功耗、更好的每瓦頻寬(Bandwidth/Watt)表現。從封裝的角度來看,Wide I/O 2晶粒(Die)是以系統單晶片(SoC)形式堆疊,藉此最小化功耗以及占用空間(Footprint)。

JEDEC指出,固有的垂直堆疊架構能允許Wide I/O 2介面在四分之一的I/O速度下,實現優於LPDDR4 DRAM四倍的頻寬。

JEDEC董事會主席Mian Quddus補充,行動裝置的革新持續推動市場上對於新一代儲存方案的需求,進一步刺激能以更小的外型,提供更高效率、低耗能的解決方案問世;他指出,JEDECJC-42.6小組委員會未來仍將致力於提供一系列行動記憶體的解決方案,期能確實切合產業界現今和未來的真正需求。