凌力爾特(Linear Technology)日前發表低相位雜訊整數N頻率合成器核心–LTC6950。元件具備超低抖動時脈分配輸出,為必須以高訊號雜訊比(SNR)來定時資料轉換器的關鍵,在資料轉換器時脈保持低抖動是數位化或合成高類比頻率時達到優異SNR的基礎。

元件內的鎖相迴路(PLL)具備卓越的歸一化頻內相位雜訊基準,或–226dBc/Hz的品質因素和非常低的-274dBc/Hz歸一化1/f相位雜訊,可於時脈分配區段保持完整。這些規範確保了設計者可充分利用被LTC6950鎖定之外部振盪器的良好相位雜訊性能,且提供同級元件中理想的抖動性能。

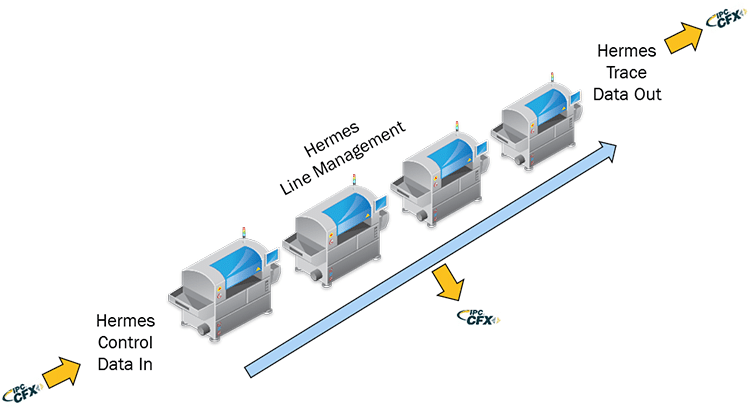

LTC6950採用專利的EZSync輸出同步,為一簡單、有效的方法以邊緣同步來自一或多個晶片的多個輸出。EZSync同步化透過簡單地斷定共同的互補式金屬氧化物半導體(CMOS)輸入來對齊升緣,對於定時的要求寬鬆。針對此功能致能之元件,EZSync同步化也可用於提供其時脈分頻器輸出間可重複和確定性的相位關係。

為簡化新產品設計流程,凌力爾特提供免費的ClockWizard模擬和設計工具,ClockWizard圖形使用者介面(GUI),可透過單次按鈕點擊來掌握迴路濾波器的元件值,並準確地預測各個輸出的相位雜訊和抖動,以協助設計人員在設計和除錯(Debug)階段進行正確的選擇。

凌力爾特網址:www.linear.com