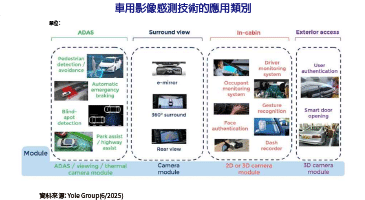

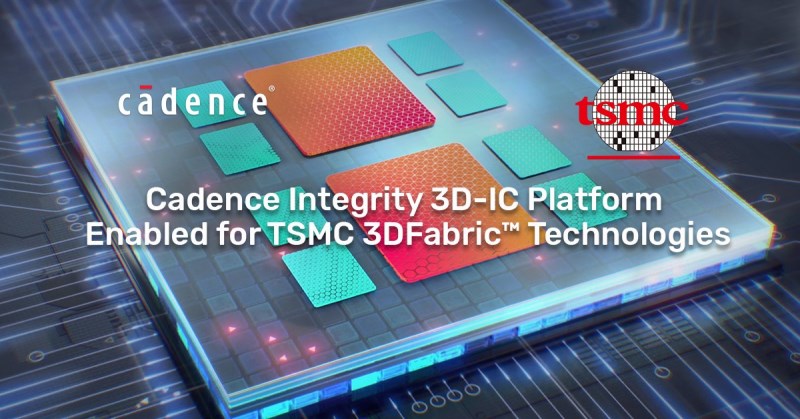

益華電腦(Cadence)宣布,該公司正與台積電緊密合作,加速3D-IC多晶片設計創新。作為合作的一部分,Cadence日前發表的Integrity 3D-IC平台是業界第一個用於3D-IC設計規劃、設計實現和系統分析的完整統一平台,此平台將支援台積電3DFabric技術,即台積電的3D矽堆疊和先進封裝的系列技術。此外,Cadence Tempus時序簽核解決方案已最佳化升級,支持新的堆疊靜態時序分析(STA) 簽核方法,從而縮短設計周轉時間。受惠於這些最新的里程碑,客戶可以放心地採用Cadence 3D-IC解決方案和台積電的3DFabric技術,來創建具有競爭力的超大規模運算、移動和汽車應用。

Cadence的3D-IC解決方案支持台積電的完整3D矽堆疊和先進封裝技術,包括InFO、CoWoS和系統級整合晶片(TSMC-SoIC )。3D-IC解決方案為Cadence智慧系統設計策略之一,推動了SoC的設計卓越。

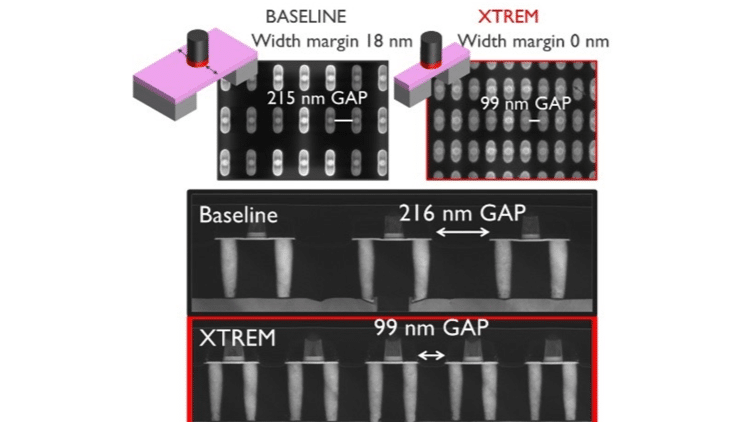

Cadence Integrity 3D-IC在一個統一的平台上中提供3D晶片和封裝規劃、實現和系統分析。這讓客戶可以簡化3D矽堆疊的多晶片設計規劃、實現和分析,同時最佳化工程生產力、功率、性能和面積(PPA)。此外,該平台還具有與Cadence Allegro封裝技術和Cadence Virtuoso平台整合的協同設計功能,可支持實現完整的3D整合和封裝。

為了進一步讓客戶受益,Cadence分析工具與Integrity 3D-IC平台緊密整合,並與TSMC 3DFabric技術無縫協作,實現系統驅動的PPA目標。 例如,Tempus時序簽核解決方案結合了快速自動芯片間(RAID)分析,這是Cadence 3D STA技術的一部分,可幫助客戶創建具有準確時序簽核的多層設計。 Cadence Celsius熱解算器支持多晶片堆疊、SoC和複雜3D-IC的分層熱分析。在分層分析中,熱點使用更精細的網格進行建模,這使客戶能夠實現運行時間和準確度目標。Cadence Voltus IC電源完整性解決方案為客戶提供熱、IR壓降和cross -die電阻分析,以實現設計穩健性。

台積電設計基礎架構管理事業部副總裁Suk Lee表示,台積電與Cadence的合作代表了Integrity 3D-IC平台以及簽核和系統分析工具支持台積電先進的3DFabric晶片整合解決方案,為我們的共同客戶提供靈活性和易用性,我們與Cadence長期合作的結果使設計人員能夠充分利用台積電先進製程和3DFabric技術在功率、效能和面積方面的顯著改進,同時加快差異化產品的創新。

Cadence資深副總裁暨數位與簽核事業群總經理滕晉慶則指出,我們正在推進與台積電的長期合作,並促進多個新興領域的設計創新,包括5G、人工智慧和物聯網。台積電的3DFabric產品與Cadence的整合式高容量Integrity 3D-IC平台、Tempus時序簽核解決方案、Allegro封裝技術和3D分析工具相結合,為我們的共同客戶提供了一個有效的解決方案來部署3D設計和分析流程,以創建強大的矽堆疊設計。