新思科技(Synopsys)針對行動裝置系統單晶片(SoC)市場,推出SoC處理器核心優化設計套件,欲以單一設計套件協助客戶設計更高效能且更低功耗的中央處理器(CPU)、圖形處理器(GPU)和數位訊號處理器(DSP)。

|

| 新思科技推出SoC優化設計套件。右為新思科技邏輯庫產品行銷經理Ken Brock、左為知識產權事業業務發展總監江偉傑。 |

新思科技邏輯庫產品行銷經理Ken Brock表示,過往無論是CPU、GPU或是DSP皆有不同的設計需求,IC設計工程師必須在效能、耗電與面積等要求中不斷權衡,且沒有一體適用(One-size-fits-all)的設計準則與工具。

Brock進一步解釋,例如CPU要求在低漏電的情況下有高效能表現、GPU則須要盡量縮小裸晶面積,同時提供低耗電及良好圖形處理表現,而DSP針對高頻段應用如基地台,需要高效能特色,但若為手持裝置應用,則須符合面積小與低耗電要求。

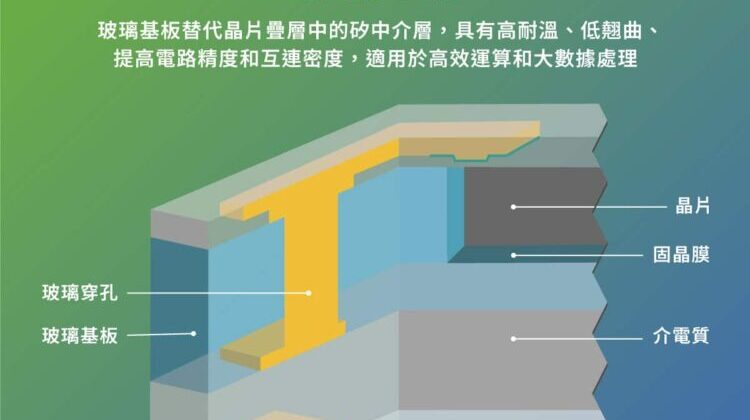

為進一步協助客戶設計行動裝置應用SoC,新思科技擴充其高效能核心(HPC)設計套件產品組合,其內容包括超高密度記憶體編譯器(Memory Complier)以及超過一百二十五個新標準元件(Standard Cell)和記憶體實體(Memory Instance),讓SoC設計人員可實現晶片內CPU、GPU及DSP矽智財(IP)核心最佳化。

Brock指出,由於GPU係平行計算架構,在使用者經驗成為行動裝置應用決戰關鍵的前提下,GPU核心為支援高畫質以及解壓縮檔案運算需求,其數量不僅增多且裸晶面積擴大,因而帶來耗電及溫度容易升高的負擔。由此可知目前GPU設計已成為行動裝置SoC設計人員最頭痛的地方,不過,新思科技的優化設計套件將能一次突破上述瓶頸。

以Imagination的Power VR Series GPU為例,該元件採用新思科技HPC設計套件的元件和記憶體,成功減少動態功耗達25%、縮小面積達10%,甚至在部分GPU區塊可實現14%的面積縮減率。

據了解,新思科技此次推出的HPC優化設計套件將主要鎖定28奈米(nm)製程,將於今年7月上市;爾後將視市場需求推出40奈米製程版本或是28奈米的低價位版本。