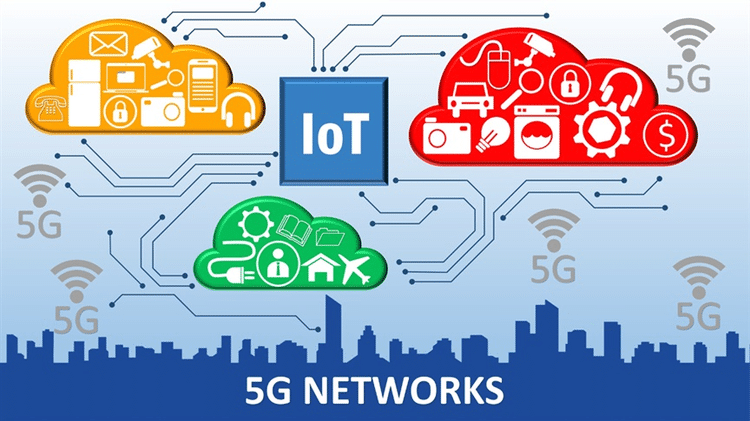

AI、自動駕駛、5G等新興應用且皆須使用高速運算、高速傳輸、低延遲、低耗能的先進功能晶片。然而,在製程微縮技術只有少數幾家晶圓代工、IC製造業者可發展的情況下,異質整合(Heterogeneous Integration Design Architecture System, HIDAS)成為IC晶片的創新動能,Chiplets便趁勢崛起,成為半導體產業熱門話題。

益華(Cadence)產品市場總監孫自君表示,人工智慧(AI)與5G快速興起,相關應用陸續浮現,成為推動半導體產業未來成長的重要動力。這些應用皆需採用高速運算、高速傳輸、低延遲、低耗能的先進功能晶片。不過,製程微縮技術變得愈來愈困難,例如為了因應各式AI應用,晶片需更高的運算效能,這使得處理器核心數量、所搭配的記憶體容量、I/O數目都急速增加,要整合的元件數量越來越多,即便是使用先進製程,要將晶片尺寸更進一步縮小仍是十分吃力。

孫自君進一步說明,即便成功小型化之後,仍還有許多要素須考量,例如功耗、散熱等。小型化意味著將各種元件整合在一起,進行運算時所產生的熱能要如何有效的散熱是一大關鍵,因為熱會影響元件電性能力;另外,要達到更好的運算效率,也意味著功率損耗愈多。換言之,晶片小型化要兼具效能、體積、低功耗、散熱等多種要素,要在這麼小的空間實現這麼多(或是做更多)的事情;若再從IP的角度思考,要將各式各樣的IP(如記憶體IP、微控制器IP、類比線路IP等)整合在一起,接著各種組合試算和驗證,所以,晶片微縮過程可說既精密又複雜,也使得造價變得更加昂貴。

孫自君指出,業者都是追求獲利,而如何降低成本是最基本的考量,在隨著晶片微縮變得越來越複雜、價格也越來越高,業者也會開始思考,究竟是不是所有晶片都需要小型化,畢竟不是所有公司都有能力投入,也不是所有應用都需要非常高的運算效能,也因此, IC設計業、晶圓代工、封裝業者轉向發展晶片小型化外的製程技術,Chiplets的概念及方式也因而開始受到關注。

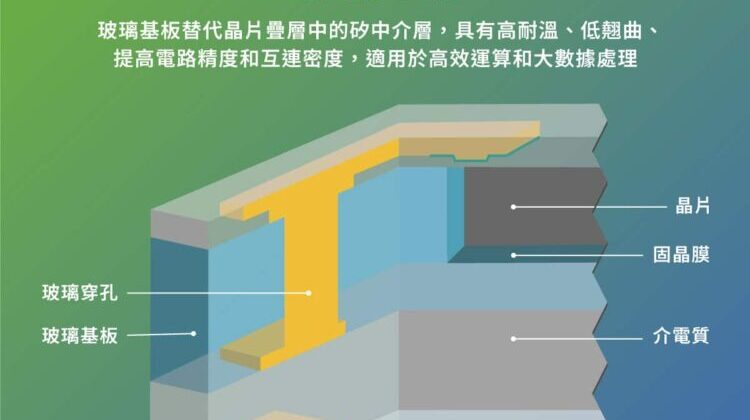

不過,要實現Chiplets系統也非輕而易舉,畢竟還是由許多晶片組成,因此在設計上仍會有許多挑戰。益華指出,使基於Chiplets成功的其中一項關鍵是確保中介層和封裝的設計正確,這些中介層將被多個高速訊號、時鐘、數據總線和地址通道填滿,才得以使訊號和電源完整性成為正確運行的必要條件。

為此,Cadence備有Sigrity/Clarity與Voltus工具,可以協助設計人員進行系統/板級與IC本體的訊號完整性和電源完整性分析。此一工具其中一項明顯優勢是包含兼顧電源的提取和分析,這對於緊密相關且基於Chiplets的系統中獲取正確結果十分重要;因為在跨IC,封裝與PCB系統的電源信號提取和分析系統中,訊號反射、串擾和同步開關噪聲很容易受到中介層電源網路中電源和接地阻抗的影響,而利用Chiplet模組化的優勢早期介入設計並納入考慮將有助於解決潛在問題減少開發的費用與時間。

而除了Sigrity,Cadence也還具有Virtuoso System Design Platform平台,該平台從電性感知布局演進至首創電性和模擬驅動布局,以確保電路完整性及效能。此一模擬驅動布局可有效解決關鍵電路和先進節點設計上的許多電電磁(EM)和寄生問題;簡而言之,該產品可供系統工程師無縫編輯並分析複雜度高的異構系統,並讓封裝、光電、類比IC和RF IC工程師在單一平台上作業。