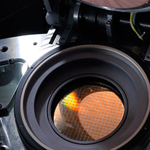

應用材料公司於國際光電工程學會(SPIE)先進微影暨圖案化技術研討會上推出一系列為滿足「埃米時代」晶片圖案化需求的產品和解決方案。隨著製程推進至2奈米以下,晶片製造商愈來愈受惠於新材料工程和量測技術,進而克服EUV和高數值孔徑EUV圖案化的挑戰,包括線邊緣粗糙度、頂端對頂端的間隙(Tip-to-tip Spacing)限制、橋接缺陷和邊緣置放誤差。

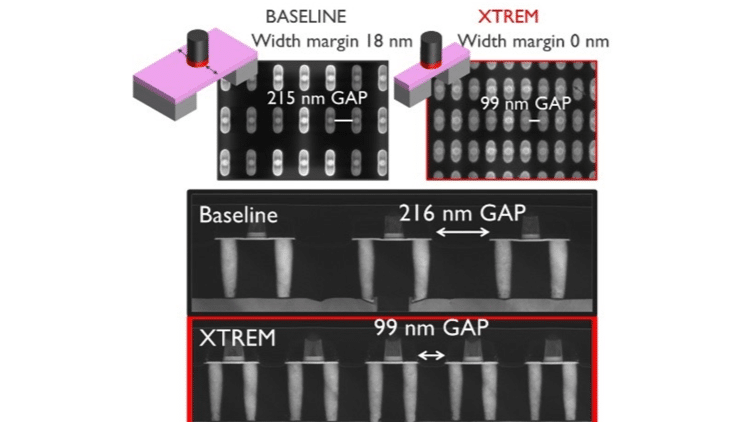

應材在2023年的SPIE微影技術研討會上推出Centura Sculpta圖案化系統,藉由這套系統,晶片製造商能夠透過延伸拉長圖案特徵來減少EUV雙重圖案化步驟,使得特徵端點彼此之間能比使用單一EUV或高數值孔徑EUV曝光更為接近。應材目前正與邏輯晶片製造商合作,開發越來越多的Sculpta應用。例如,除了減少頂端對頂端的間隙外,晶片製造商也使用Sculpta來消除橋接缺陷,進而降低圖案化成本並提高晶片良率。

應用材料公司半導體產品事業群總裁Prabu Raja博士表示,晶片製造商已在生產過程中部署Sculpta系統,並持續探索減少EUV 雙重圖案化步驟之外更多的應用。Sculpta是圖案化工程師機台套件中的全新機台,藉此工程師能夠發揮想像,運用嶄新的方法來解決充滿挑戰性的問題。

英特爾公司邏輯技術開發部副總裁Ryan Russell表示,圖案成形是協助英特爾加快推進製程技術藍圖的創新解決方案。英特爾為埃米製程節點部署Sculpta系統,初步結果顯示產能增加、晶圓良率提高,且製程複雜度和成本降低。圖案成形促進了先進圖案化新策略,也為突破微影印刷極限開創可能。

三星電子代工蝕刻技術團隊主管朴鐘澈表示,圖案成形為一項突破性技術,可解決EUV世代的關鍵挑戰。三星身為早期開發合作夥伴,正在評估適用於4奈米製程的Sculpta系統,期待能得到包括降低成本、複雜度以及提高良率等正面成果。

EUV系統產生較少可以被用來清楚定義光阻中線條和空間圖案的光子,這會導致邊緣粗糙的圖案線條被蝕刻到晶圓上,有機會造成晶片中的開路和短路。隨著晶片製造商在埃米時代採用更窄的線路和空間圖案進行設計,這些會影響良率的缺陷將變得越來越常見。

應材推出Sym3 Y Magnum蝕刻系統,可在同一反應室中結合沉積和蝕刻技術。這套獨特系統沿著粗糙邊緣沉積材料,使EUV線路圖案在被蝕刻到晶圓前變得更平順,進而提高良率並降低線路電阻,進而改善晶片效能和功耗。在邏輯晶圓代工產業,已有晶片製造商採用Sym3 Y Magnum進行關鍵蝕刻應用,目前正部署用於埃米時代節點中的EUV圖案化;在記憶體產業,Sym3 Y Magnum是DRAM中用於EUV圖案化被廣泛採用的蝕刻技術。

應材推出Producer XP Pioneer CVD(化學氣相沉積)圖案化薄膜,在進行光阻圖案處理前將Pioneer薄膜沉積在晶圓上,獨特設計可將所需圖案以卓越的保真度轉移到晶圓上。Pioneer採用獨特的高密度碳配方,對先進的製程節點中使用的蝕刻化學物質更具彈性,讓厚度更薄的薄膜堆疊具備卓越的側壁特徵均勻度。Pioneer已被記憶體製造商採用於DRAM圖案化。

Pioneer已經與應材的Sculpta圖案成形技術進行共同最佳化,使圖案工程師能盡量延伸圖案,同時保持對原始EUV圖案的嚴格控制。Pioneer也與全新的Sym3 Y Magnum蝕刻系統進行共同最佳化,為邏輯和記憶體製程中的關鍵蝕刻應用提供比傳統碳薄膜更高的選擇性與更良好的控制。

應材的電子束量測系統,由邏輯和記憶體公司採用於開發和控制最關鍵的EUV圖案化應用,其中一個主要挑戰是要嚴格定義並將數十億個特徵放置在每一層,使之與晶片中下一層的相反特徵正確對齊。微幅的置放誤差會降低晶片效能和功耗表現,而大幅度誤差更將造成影響良率的缺陷。

應材已收購Aselta Nanographics,此公司具備使用輪廓進行設計型量測的技術專業。圖案化工程師能夠透過輪廓收集更龐大的數據量,了解他們的配方在圖案化薄膜和晶圓上製造出的形狀,並且將這些資料回饋至光學微影和製程流程,以製造更精確的晶片特徵和置放位置。

應用材料公司影像和製程控制集團副總裁Keith Wells表示,Aselta輪廓技術現已與應材的VeritySEM CD-SEM系統和PROVision電子束量測系統進行整合,為晶片製造商提供端到端功能,可解決埃米時代全面向的量測挑戰。

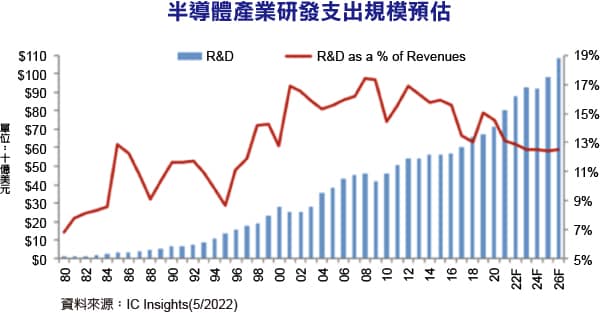

自2012年以來,應用材料公司優先將圖案化作為研發重點,投資推出新產品和解決方案,幫助客戶克服最棘手的圖案化挑戰,特別是在新興的EUV和高數值孔徑EUV應用領域。應材目前的圖案化產品組合包括CVD和ALD沉積;四種材料去除方法(蝕刻、選擇性材料去除、圖案成形和CMP);熱處理製程和電子束量測。應材已將其服務的圖案化市場從2013年約15億美元增加到2023年超過80億美元,並在同一時期將機會市占率從約10%增加到超過30%。