掌握四大功耗類型 FPGA耗電管理輕鬆上手

系統設計人員現今被迫針對最低功耗進行系統設計,尤其是使用FPGA元件。為了最大限度地降低FPGA元件的功耗,系統設計人員應當全面考慮它的總體功耗,主要有:

.配置

.靜態電流(Static Current)

.動態電流(Dynamic Current)

現在,讓我們來細看每一項功耗的因素:

挑選FPGA元件 浪湧/上電電流須注意

當FPGA元件上電時,必須建立內部偏流(Bias)和完成重定順序,其引起的電流浪湧可能會產生高達數安培、長達數百微秒的電流尖波,從而帶來浪湧功率。

FPGA元件供應商通常不會強調這種功率成分,不過,它在影響電源設計、總體系統成本和實際空間要求方面,扮演非常重要的角色。在毋需頻繁進行電力循環的系統應用中,上電電流對總體功率的影響較小;然而,在需要頻繁電力循環的應用中,上電電流本身就是很大的功率消耗。

除了總體功耗,暫態功耗也是上電電流帶來的挑戰。上電電流比FPGA元件的運作電流高出數倍,這須要特別設計的電源來提供上電所需的電流。此外,建基於SRAM的FPGA元件需要上電排序,而且不遵從上電順序可能引起上電電流遠高於元件資料表中所記載的資料。這進一步增加了上電順序電路的需求,因而帶來了額外的成本和實際空間需求。

考慮過所有這些因素後,在為任何系統挑選FPGA元件之前,最重要的是先瞭解上電電流的規範,建基於快閃記憶體的FPGA元件對於低功耗設計具有顯著的優勢,比如無浪湧電流尖波、簡化的上電重定(POR)順序及較低的總體電源成本。

配置電流

建基於SRAM的FPGA元件在失去電源時不會保留配置資料,必需在上電時從外部的非揮發性記憶體重新上載配置資料,這會在數百毫秒(msec)間消耗掉大量的電流,並且可能使得具有頻繁電力循環的系統的電池壽命縮短。建基於快閃記憶體的FPGA元件在電源切斷後仍可以保持配置,因而毋須消耗任何配置電流。

靜態電流(Static Current)

靜態的電流消耗也稱作靜態電流(Quiescent Current),它是因為電晶體中的洩漏所造成的。對整體系統功耗而言,靜態功耗是非常重要的,因為它是元件在被供電期間必定會消耗的恆定功率(如果沒有低功率模式)。靜態功率與開關頻率無關,因而在以低頻率運作的系統中,必須仔細考慮,以降低動態功耗。在這樣的設計中,靜態功率將占據總體功耗的主要部分。

建基於SRAM的FPGA由每單元具有六個電晶體的SRAM單元構成,具有多個洩漏路徑,因而每單元的洩漏電流較大,並具有高靜態電流。相比之下,建基於快閃記憶體的FPGA元件僅由一個每單元洩漏電流降低1000倍的電晶體所構成,因此具有超低的靜態功耗。

動態電流

動態的FPGA功耗是:

P = CV2F

其中

P=以W為單位的動態功耗

V=以V為單位的運作電壓

F=以kHz為單位的頻率

C=以μF為單位的負載電容

較高的運作頻率會帶來較高的動態功耗,在為系統挑選元件之前進行功率估算是非常重要的。所有FPGA供應商都會提供估算器來估算建基於資源使用和開關頻率的動態功率。

上述所有功率元件均對總體功率有影響,在元件上電時,上電電流會影響總體系統功耗,可能達到數百mA,或者在較高密度FPGA元件中達到數安培。在系統上電時,靜態和動態功率決定了功率預算。從系統的角度來看,在平均功耗較高的情況下,熱管理也是一個挑戰。在這樣的場合下,如果熱管理被忽略,可能會引起熱耗散。

對於正常工作時間幾乎為100%的系統來說,比如大多數伺服器應用,靜態和動態功率是最重要的檢驗項目。然而,如果元件在較高的頻率下運作,動態功耗便會在總體功耗中占據主導地位。

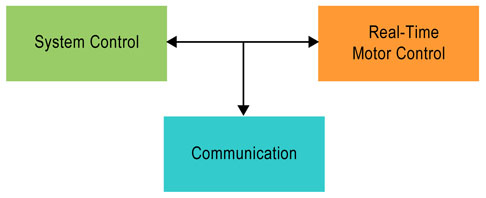

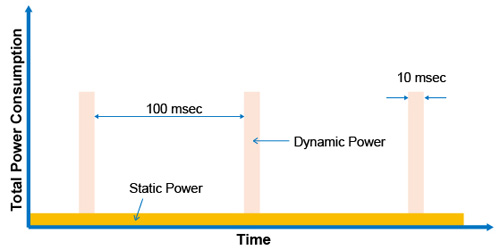

讓我們以一個須要捕獲和處理一些資料,然後傳送給主機設備的遠端感測器節點作為對照的例子。在這樣的應用中,邏輯部分毋須一直開關,這是因為元件能夠抽樣資料、進行處理、傳送,然後,邏輯可以利用閘控時鐘來避免切換,直到須要處理另一個樣本。圖1所示為此這一類系統的功率分析,工作時間大約為10毫秒,然後是大約100毫秒的休眠時間。

|

| 圖1 動態電流系統功率分析圖 |

滿足低工作週期運作 靜態功率不可缺

滿足低工作週期運作 靜態功率不可缺

在這樣的應用中,靜態功率是影響總體系統功率的主要因素,因此,在這類應用中必須選擇靜態功率低的元件。此外,還要考慮讓元件在較低頻率下運作,而不是猝發模式(Burst Mode)。系統設計要分析上述兩種場景,然後選擇最適合該系統的元件。

低功率模式有助於進一步降低FPGA元件的功耗。包括睡眠和深度睡眠等等的低功率模式,它們在微控制元件中是眾所周知的。一些FPGA元件也同樣支援某些形式的低功率模式,這對於需要低工作週期運作的應用是有幫助的。

這些模式的可用性取決於幾個因素,比如在低功率模式下節省的功率、從一種功率模式轉移到另一種功率模式的轉換時間、設計複雜性等等。建基於SRAM的FPGA元件在退出低功率模式時須要重新配置,從而帶來較長的退出時間。它會在重新配置時引起電流浪湧,而且暫存器資料會在電源切斷期間遺失。

然而,這些模式在某些應用中十分實用,我們應該仔細瞭解。一些建基於快閃記憶體的FPGA元件(比如IGLOO、IGLOO2和SmartFusion2元件)可支援快閃Freeze模式,允許元件進入超低功率模式,同時保持SRAM內容、I/O狀態,以及暫存器資料。根據元件系列,可以使用I/O活動、I/O簽名匹配或RTC喚醒中斷等各種來源來退出快閃Freeze模式,而且毋需外部時鐘進行RTC時間保持。

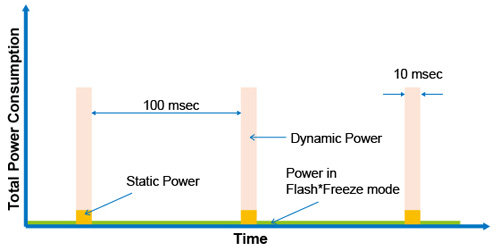

在快閃Freeze模式中,內部時鐘電路是處於電源切斷的狀態,進入和退出時間幾乎可以忽略,因此退出需要的時間主要為上電時PLL鎖定時間,這個時間<100微秒。圖2所示為使用快閃Freeze模式時的功率分析。然而,它沒有考慮進入和退出時間,因為這在建基於快閃記憶體的FPGA元件中是可以忽略的。

|

| 圖2 快閃Freeze模式功率分析圖 |

另外,輸入/輸出引腳是主要的功率消耗之所在。I/O功耗取決於負載、旋轉率(Slew Rate)和驅動強度。支援可配置旋轉率和驅動強度的元件,能夠顯著幫助降低總體系統功率。低電壓I/O標準也有助於減小功耗。

硬IP助力 FPGA元件功耗再降低

硬IP(智慧財產權)在功率和實際空間要求方面進行最佳化。有些IP經常用於UART、I2C、SPI、DDR控制器、串列收發器或SERDES、PCIe等等應用。取決於不同應用,最好是找到具有硬IP的元件,並且在比較兩款元件時,應當分析每個IP的功率。

例如SERDES在應用中會消耗大量功率。一些FPGA元件具有低功率SERDES收發器,比如SmartFusion2和IGLOO2元件,這些元件已針對功率而最佳化了,功耗比其他FPGA元件降低多達五倍。

對於硬IP,瞭解實際系統需求也很重要,這樣能夠幫助挑選只有所需硬IP的元件,確保你不會因為不需要的功能而付出更高費用,並且盡可能地降低耗電量需求。一個最好的例子是某些FPGA元件提供的高階應用處理器,雖然這些處理器在計算密集應用中有用,但如果它們只使用一段短時間,或在較低的頻率下運作,就會增添巨大的靜態功率。例如,具有A9處理器核心的SoC元件在所支援的溫度範圍會增加多達700mA的靜態電流。

軟體開發工具助力 低功率產品開發時程大幅縮短

在進行低功率產品設計時,軟體開發工具能夠顯著影響產品的開發週期,如果開發工具具有估算功耗的功能,並提供易於使用的選項來最佳化總體功率,以及輕易接入矽元件提供的低功率模式,便可以簡化設計人員的工作,並且縮短對於現今競爭激烈市場十分重要的開發時間。

幾乎每個主要的FPGA供應商的開發工具均支援功率估算功能,例如,美高森美提供的SmartPower工具具有詳細準確的設計分析方法,還提供頂層總結,以及較低層的特定功能之功耗分析,比如閘極、網路、I/O、記憶體、時鐘域、區塊(Block)和電源軌。

為了實現低功耗系統設計,記得要挑選是為低功率下運作所設計的元件,這是很重要的;此外,還必須獨立地考慮上電電流、配置電流、靜態電流,以及動態電流,還要進行功率剖析以瞭解每個功率元件對於總體系統功率的影響。在功耗方面,建基於快閃記憶體的FPGA元件具有超越建基於SRAM的FPGA元件的固有優勢。

低功率模式是有用的,在系統毋需100%時間處於工作狀態的應用中,能夠節省大量功率。具有豐富的硬IP的元件能夠進一步降低靜態和動態功耗。具有實現低功率系統設計功能的開發工具,將有助於以較低的開發成本和更短的上市時間實現高功效系統。