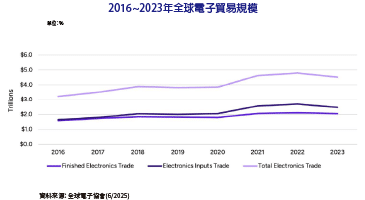

在生成式AI的帶動下,電源產業正在經歷一場翻天覆地的革命。從元件所使用的材料到測試/驗證,甚至供電網路的設計,許多新技術、新概念正在快速發展。

被稱為「吃電怪獸」的生成式AI,為電源供應器產業帶來巨大的商機及挑戰。為滿足AI資料中心對電源效率與功率密度的要求,電源產業必須一改過去保守穩健的作風,大膽擁抱新技術。不管是採用碳化矽(SiC)、氮化鎵(GaN)等寬能隙元件,或是改變電源設計架構,甚至將負載點(POL)電源與處理器共同封裝,都是很好的例子。

東芝跨足GaN 2026年布局到位

東芝(Toshiba)電子工程部經理上新原崇(圖1)指出,矽、碳化矽(SiC)和氮化鎵(GaN)這三種半導體材料都可以用來製作功率元件,但各自有不同的應用場景。矽元件最為成熟,但在需要高額定電壓與高頻操作的應用方面,存在許多先天局限,SiC能在高電壓與相對高開關頻率的條件下操作,GaN則最適合用在高開關頻率的應用。

因此,針對SiC元件,東芝鎖定的應用市場是高電壓和高電流應用,如風能、鐵路、太陽能等,而氮化鎵元件則適合於伺服器和電信設備的電源供應器、各種消費性應用及光達(LiDAR)的電源供應。

不過,隨著伺服器的功率需求持續上升,在伺服器電源應用領域,SiC跟GaN都有應用的機會。例如在伺服器電源的功率因素校正(PFC)與一次側,東芝除了提供SiC蕭特基二極體(SBD)跟SiC MOSFET之外,同時也在開發基於GaN的產品。

接著,上新原提到東芝分立式碳化矽MOSFET的最新進展,及相較競爭對手的優勢。上新原表示,東芝第三代碳化矽MOSFET最大的特色在於穩定。與市面上其他競爭產品相比,其效率隨溫度的變化程度是最平穩的,同時死區時間(Dead Time)損耗的表現也最為優秀。

至於在GaN元件部分,東芝預計自2025年第一季起,陸續提供相關樣品給客戶測試。先從整合型的Pch GaN驅動IC開始,到2026年,東芝將推出首款常關型(Normally-off) GaN開關元件,目前市場上尚無其他競爭對手提供類似的產品。此後,東芝在GaN領域將推出兩個產品家族,其中之一是整合驅動IC與常關型GaN元件的產品,另一個產品家族則是單純的常關型GaN元件。

功率密度驅動GaN發展前景

在GaN電源應用領域耕耘已有十多年歷史的德州儀器(TI),則認為在伺服器應用市場上,GaN適合高頻操作的特性,將使GaN成為更具優勢的技術。

德州儀器應用工程師王俊昇指出,隨著AI資料中心的用電量持續增加,資料中心的擁有者對於能源效率跟功率密度的要求,正變得越來越嚴格。在這個背景下,能夠高頻操作而且能源轉換效率極佳的GaN,正受到越來越多資料中心客戶的青睞。

而為了加速電源設計工程師的研發速度,TI不僅提供元件,還有各式各樣的參考設計。讓電源工程師能夠用更短時間開發出符合客戶或業界標準要求的產品。例如在圖騰柱(Totem-Pole) PFC方面,TI已經提出4kW單相與5kW雙相參考設計,4kW的參考設計更被OCP及Europe 80 Plus Titanium選為參考方案。

展望未來,TI將繼續擴張GaN產品線,從目前主流的650V向下延伸至100V與200V,打造業界涵蓋面最完整的GaN產品家族。同時,為確保穩定供貨能力,TI也會在產能方面不斷進行投資。

大電流/低電壓趨勢考驗電源完整性

AI應用的興起除了影響PSU的設計外,同樣也對DC-DC及主機板上的電源設計帶來新挑戰。

克達應用工程經理馮育隆(圖2)認為,當前在DC-DC部分,電源設計工程師所遇到的挑戰,都跟晶片的電源需求有關。不管是GPU、FPGA或ASIC,使用先進製程製造的晶片,其搭配的配電網路(PDN)電壓越來越低,但消耗的電流卻明顯增加,這使得DC-DC電路的輸出必須極為精準而且穩定,而且電源受雜訊干擾的風險也不斷上升。

而且,上述電源完整性(PI)的問題若沒有妥善處理,還會進一步影響到訊號完整性(SI)。伺服器裡面有很多高速介面,其訊號完整性問題往往跟電源完整性有密不可分的關係。要提高PDN的電源完整性,有很多事情要做。從量測的角度,我們需要改善DC-DC轉換器的反饋迴路電路,以提高迴路穩定性和負載變化的瞬態響應速度的平衡。 這是提高電源完整性的基礎。

此外,現在變得非常重要的另一個重點是PDN阻抗。 這裡讓我們假設總PDN的阻抗為Zpdn。 通過將Zpdn抑製到非常小的值,如毫歐姆等級,就可以將Vdd的變化降到最低,漣波值自然就變小了。

但在實務上,要將阻抗降到微歐姆,就已經是很有挑戰性的目標,因為一般的量測手法與設備很難量測到這麼低的阻抗值。是德(Keysights)的15061B系列的網路分析儀可以解決這個問題。該儀器具有低頻(5Hz起)的測試能力,能夠有效監測接近DC狀態,並提供準確的阻抗值的讀數。他還強調了選擇電容的重要性,比如低等效串聯電阻(ESR)電容對於降低漣波,能帶來相當顯著的效果。

在漣波測試部分,最大的挑戰來自於探棒(Probe)跟示波器本身的雜訊。不管是10:1被動探棒、1:1被動探棒或同軸電纜,都有各自的問題。因此,針對PI量測,還是需要使用專門的電源軌探棒。

追求效率極限 電源/處理器共同封裝

使用先進製程的AI晶片,除了帶來電源完整性的挑戰外,同時也增加了電源傳輸過程的損耗。由於AI晶片需要的電流最高可達數百,甚至上千安培,因此,在電源傳輸的過程中,線路損耗變成一個不容忽視的課題。

Vicor資深技術支援工程師張仁程(圖3)指出,由於最先進的AI晶片往往需要破千安培電流,其線路損耗非常可觀,因此,如何縮短主機板上穩壓器(VR)與處理器之間的距離,也是當前業界關注的技術議題。

Vicor從很多年前就已經開始關注這個技術趨勢,並提出分比式電源(Factorized Power)與垂直電源的概念,讓電源模組可以在不干擾處理器運作的前提下,盡可能配置在距離處理器最接近的位置,甚至是處理器的封裝基板背面。

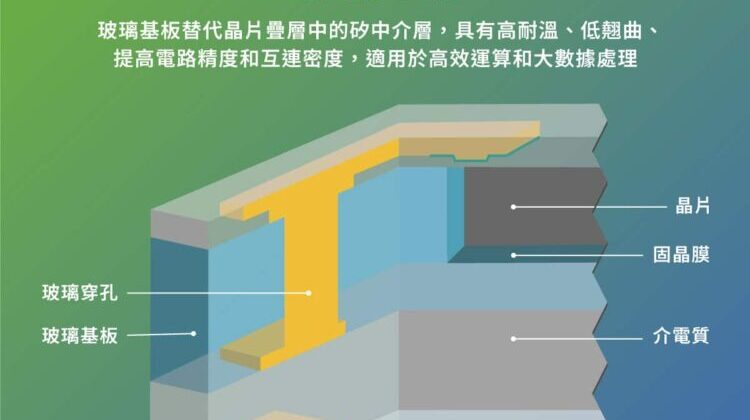

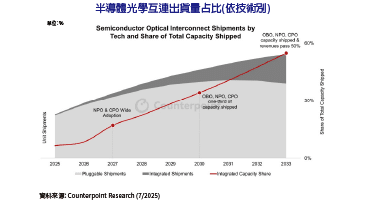

經過多年演進,Vicor已經先後與不同客戶、合作夥伴驗證過這個想法的可行性,甚至有量產的實績。而隨著技術越來越成熟,現在Vicor有一部分模組產品已經可以與處理器實現垂直共同封裝,不再只是配置在處理器的側面。這種設計也可以把寶貴的基板空間讓出來,讓光學共同封裝(CPO)的I/O有地方可以配置。同時,Vicor也已經開始挑戰下一個目標:把電源模組嵌入封裝基板,甚至是配置在中介層(Interposer)下方,以進一步縮短處理器與電源模組之間的實體距離。