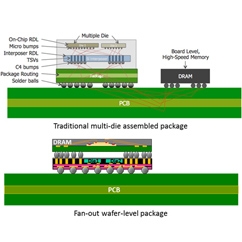

現今半導體構裝技術為了因應可攜式電子產品的輕薄短小化、光電通訊產品的高速化、微系統產品的高度整合之需求及環境保護的強烈需求下,須開發更先進的微連結技術,如提高覆晶接腳密度、採用三維(3D)堆疊構裝、超薄膜覆晶構裝、配合環保的無鉛覆晶構裝及微系統密封構裝以因應未來整合度高的光電通訊、微系統、攜帶式電子產品。

3D整合系統構裝展現3D IC晶片面積的縮減,並能做到最佳化的劃分,這兩個優點使整個系統的製作成本能夠降低,此外,3D構裝尚有一個優點是能縮減連結線路的長度及消除晶片間傳輸速度的限制。由於體積的縮小及重量的減輕,使此系統具有較低的功率損耗,並能在可攜式電子產品具有應用潛力。但隨著半導體製程技術的演進,已由多年前的1.0毫米製程演進至現階段0.15、0.13毫米甚至是奈米製程的開發,其技術的開發速度極為快速。原則上,以摩爾定律之半導體製程技術在每十八個月可讓單位面積上的電晶體成長一倍,但也使其物理上的極限提早來到,將無法有效的提升其效能,如同建築物的發展模式,面內的發展受到限制後(半導體製程極限),則開始面外的發展(3D堆疊技術)。

而現階段的3D堆疊構裝大多是以打線接合(Wire Bonding)為基礎製作,幾乎面臨瓶頸,已無法更一步的發展,因此將晶圓以穿孔式,即直通矽穿孔技術(Through Silicon Via, TSV)導通進行堆疊的技術,有機會解決現今打線技術所遭遇之問題,並提升系統之效能。

3D IC技術提升晶片整合度

世界上已有許多公司及研究機構致力於發展3D系統之整合技術,目前除利用再結晶或磊晶方式成長具有不同功能的矽層外,最主要還是利用構裝技術達到3D系統整合,可歸為三類:

| 具有可針對IC元件先進行預測、不會產已知良裸晶粒(Known Good Die, KGD)的問題、有較高的封裝良率等優點。 |

| 具有較短的導線距離、較佳電性,再加上沒有晶片的預封裝,可獲得更薄型化的效果。 |

| 具備晶片尺寸型封裝(CSP)、薄型封裝,且封裝成本較傳統法低、可靠性高、散熱性佳(熱傳導路徑短)、電性優良(封裝的走線短,使得電感及電容低)等優點。 相較之下,目前較容易達到3D堆疊的構裝技術是晶片堆疊,之後再利用打線的方式將電性及訊號與基材連結,正如導線架的封裝一般,目前以封裝三片晶片以上為市場主流。 |

上述立體堆疊技術,各有各的優勢與應用的方向,若以上下元件連接的方式區分,可區分為導通孔的連接、側壁的連接方式與打線接合的連接方式,同時亦可分為凸塊(Bump)的連接方式與無凸塊(Bumpless)的連接方式。在連接的介質方面更是多樣化,有金屬對金屬的接合、膠材的接合、與矽晶圓之矽或二氧化矽的直接接合(Direct Bonding),當然也有金(Au)、矽(Si)的共晶接合等技術,這些不同的接合方式,無非都是想要連接上下的訊號,如能再搭配晶圓薄化技術,除可以最短的封裝距離達到尺寸與電性的最佳化外,更可在有限的空間裡放進更多的元件,增加構裝密度。

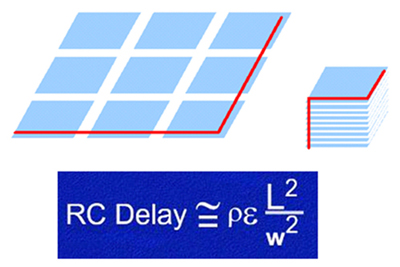

圖1為半導體不同世代之時間延遲關係圖,圖中顯示要達成多功能的晶片,須精進半導體製程技術,以在相同大小的晶圓上製作出更多的電晶體,但在縮小線寬、線距的同時,卻因為金屬導線截面積縮小、長度增加而造成金屬導線的RC延遲時間趨於嚴重,一般相信在90奈米世代以後,RC延遲時間將超過閘極(Gate)延遲,成為影響元件運算效能的主要原因。即使使用銅(Cu)及Low K材料,改善程度仍然有限,由以上趨勢可以發現,新的IC封裝技術須能夠提供更小的封裝體積及更高的效能。

|

| 圖1 半導體不同世代之時間延遲關係圖 |

除了採用Low K材料降低RC延遲之外,3D IC技術也提供一個很好的解決辦法,圖2說明3D IC封裝與傳統平面封裝最大差異在於導線的長度大幅縮減,導線經由TSV直接穿過晶片與下層接點導通,因此能藉由縮短導線長度大幅降低RC延遲問題,達到更小的封裝體積、更高的效能及較低的能量損耗等優點,相當適合應用在多功能及高效能需求的攜帶型電子產品應用上。

|

| 圖2 3D IC示意圖 |

立體堆疊技術多軸發展

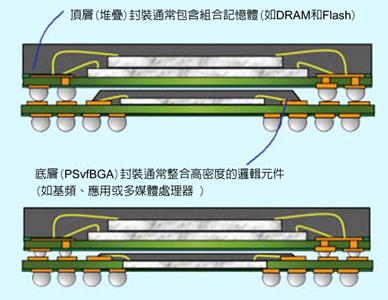

如上所述,隨著電子元件的微小化,高密度化,由原本二維(2D)的構裝演進到3D的堆疊構裝,主要被使用的有層疊封裝(Package on Package, POP)、疊晶(Chip on Chip, COC)、晶片堆疊晶圓(Chip on Wafer, COW)與晶圓堆疊晶圓(Wafer on Wafer, WOW)四種堆疊的形式。POP如圖3所示,分別將已經完成個別封裝的部分進行堆疊的動作,此堆疊技術的優點在於製程穩定、良率高,但因為如此的堆疊方式,體積較大,電信傳輸距離較長,所以較難應用於高頻的電子元件與須微小化的電子元件。

|

| 圖3 POP堆疊架構 |

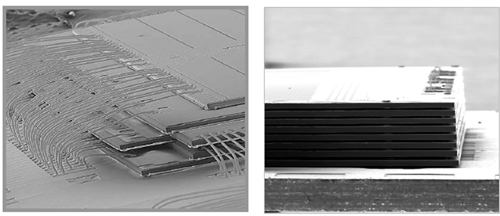

而COC、COW均是將晶片透過Face-up或Face-down的接合方式,將上方的晶片與下方的晶片或晶圓進行接合,如圖4所示,左為Face-up的例子,透過打線接合連接上下的訊號;右為Face-down的例子,透過TSV加上微凸塊(Micro-bump)連接上下的訊號。優點在於電性傳輸路徑短,可用於高頻需求的電子元件上,且體積小,沒有KGD的問題,不過因為要將單顆的晶片逐一執行堆疊的製程,所以量產速率降低,良率亦不高。因應其量產速率降低的因素,所以有批次接合(Batch Bonding)的技術出現,此技術是先將晶片精準的放置於一搭載的基板上,最後再將此基板與另一端的晶圓進行接合,此技術的好處在於可以一次完成全部的接合製程,但其對位的精準度則是一項大考驗。

|

| 圖4 COC與COW堆疊架構 |

而WOW則是晶圓跟晶圓直接的對接,所以不僅兩晶圓的樣式要互相搭配,其尺寸大小也要互相配合,所以限制最多,不過如果撘配前段晶圓的設計加上有高製程良率的晶圓,此方式的接合則是最為經濟且最快速的接合方式,目前應用較多的領域是在記憶體的方面,而就目前市場面來觀看,COC或是COW還是占較重要的地位,應用上也比較廣泛。

薄晶圓處理為3D IC製程重要關鍵

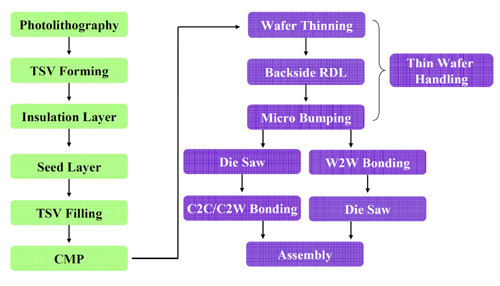

圖5為基本的3D IC製程步驟,首先以黃光光阻製程定義出導通孔位置,接著以蝕刻方式包括深反應式離子蝕刻(DRIE)、雷射、濕式蝕刻(Wet Etching)等蝕刻出導通孔,然後以成長金屬(Metal)作為擴散阻擋層(Diffusion Barrier Layer)及電鍍底電極,接著為導通孔電鍍製程及化學機械研磨(CMP)製程,最後是接合製程。

|

| 圖5 3DIC製程步驟 |

依據Yole Developpment的統計,在蝕刻製程上,約有95%使用DRIE,其通孔大小以1~10微米(μm)占多數,導通孔材料以銅為主,占62%;而接合則以膠材及金屬接合為主,分別占45%、37%。

其中,薄晶圓處理技術在3D IC製程中是相當關鍵且重要的技術,由於晶片與基板接合後須進行晶圓減薄製程,因此這個接合的接面須能承受研磨及CMP的力量而不能脫離,且由於晶片邊緣形狀在研磨後會成銳利之角度,因此接合接面也須完全支撐晶圓邊緣,將其保護住增加晶圓強度使其不會發生破裂情形。另外,由於晶圓減薄之後還須經過許多後續製程,因此接合材料必須具備相當之耐熱及耐化性,以免在製程中分離導致晶片破壞。最後,在晶圓分離時,也希望能有較高的分離速度、較低的分離溫度、較小的應力及較少的設備投資。

廠商已進行3D IC產品應用開發

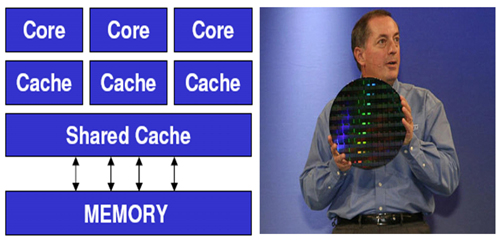

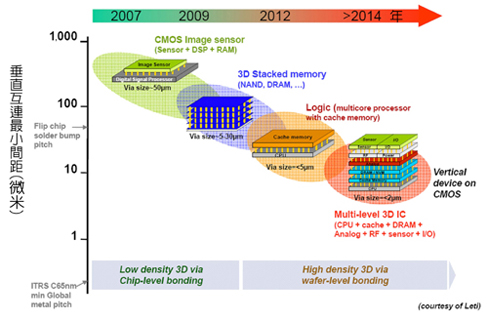

圖6為Leti提出之3D IC產品應用發展趨勢,由此可了解目前3D IC使用100微米間距的TSV,屬於低密度3D穿孔晶片級接合(Low Density 3D Via Chip-level Bonding),其第一個應用產品為互補式金屬氧化物半導體影像感測器(CMOS Image Sensor, CIS),包含單獨的CIS利用TSV封裝或將CIS與數位訊號處理器(DSP)加隨機存取記憶體(RAM)進行堆疊。而2008年後,產品應用推到3D堆疊記憶體(Stacked Memory),包含NAND、動態隨機存取記憶體(DRAM)等,接下來則是間距更小的高密度3D穿孔晶圓級接合(High Density 3D Via Wafer-level Bonding),屬於邏輯(Logic)的堆疊,如多核心處理器(Multi-core Processor)與高速緩衝記憶體(Cache Memory)的堆疊,最後,則是各種不同晶片的整合,如中央處理器(CPU)+Cache+DRAM+類比(Analog)+射頻(RF)+感測器(Sensor)+輸入/輸出(I/O)的整合封裝。以下介紹各廠商3D IC產品研發情況。

|

| 圖6 2007~2014年3D IC產品應用發展趨勢 |

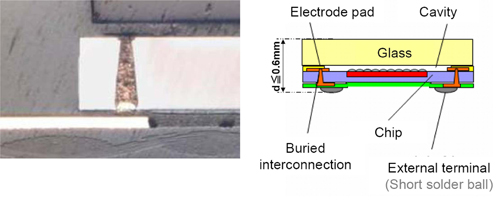

ZyCube影像感測器封裝利用3D IC技術改善傳統製程的良率問題。傳統製程首先將晶圓依切割道切割成一個個晶粒,接著進行打線封裝,最後才蓋上蓋玻片(Cover Glass),在晶片切割過程中由於較低的無塵室環境及切割造成的污染,使得顆粒(Particle)發生問題,導致良率下降。ZyCube應用3D IC TSV技術,於晶圓製作完成後,在較高等級的無塵室中直接蓋上蓋玻片,再由晶圓後方將電信利用TSV傳遞出來,透過錫球與電路板做連接,其結構如圖7所示。

|

| 2006年4月三星(Samsung)發表利用3D IC技術堆疊八層2Gbit NAND記憶體,達成共16Gbit的記憶容量,而其堆疊完的厚度僅560微米,甚至比原始8吋晶圓還要薄,這種高密度的記憶體封裝,對於攜帶型產品高記憶容量的需求(存放音樂、照片、電影動畫)非常必要,一般來說大容量記憶需求的產品有主要使用於電腦上的固態硬碟(SSD),以及使用於手持裝置的記憶卡等。 |

| 在邏輯+RAM應用方面,英特爾(Intel)在2006年宣稱將利用TSV技術達成80核 心的CPU,其處理器與記憶體間的傳輸速度將高達TBit/s的等級,並預計於2011年開始量產。其概略架構如圖8所示。應用3D IC技術能大幅增加快取容量,並提供良好的電信表現,使整體CPU效能能夠大幅度提升,雖然這將節省許多的記憶體空間,但是必須製作出數以百萬的TSV,技術困難度相當高。

|

3D IC市場規模龐大

Yole Developpment對3D IC市場所做的預測分析指出,2008年開始,短期內會是縮裝的需求,應用在攜帶型電子產品上則為記憶容量的增加,以及尺寸的縮小,在有限的空間中堆疊更多的晶片。中期的市場將於2010年開始,其驅動力來源為高效能的需求,具有更高的傳輸速率以及減少寄生功耗,此時期將有較多的異質晶片整合,如RF+邏輯+記憶體+感測器等。長期的市場驅動力將往低成本方向考量,預估在2012年開始,3D IC技術開發成本將有機會比其他競爭技術更低。

根據Yole Developpment的觀點,在相同晶片堆疊下,即使堆疊層數高於八層,其製作成本仍高,但是若將異質晶片藉由3D IC技術堆疊,其帶來的效能優勢及封裝後尺寸的減小,將大幅增加3D IC的市場競爭力。

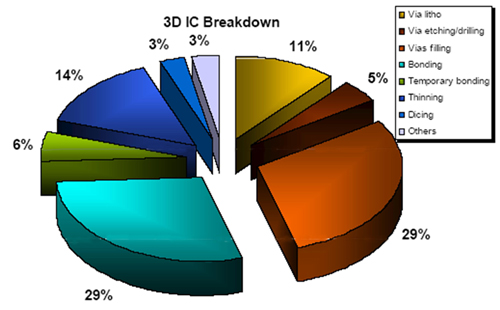

圖9顯示3D IC TSV製作之個別製程成本估算,其中占最大比例的為填孔(Via Filling)及接合製程,填孔由於高深寬比電鍍須使用特殊設計之電鍍設備及鍍液,且電鍍時間往往相當長,部分研究單位甚至需要6小時以上的電鍍時間,才能完成Void Free TSV電鍍,因此在填孔上造成成本上升。而在接合方面,金屬與金屬接合往往需要精密的對位設備,且部分金屬於接合後也需耗時的退火製程,造成時間成本增加,至於晶圓接合晶圓(Wafer to Wafer)或晶片接合晶圓(Chip to Wafer)的成本比較,Yole Developpment認為2009年之前,後者製作成本較高,但是在2012年後,因為設備的改善,這兩種方式製作成本均會下降,且兩者差異不大。

|

| 圖9 TSV成本估算 |

近期內利用3D IC技術的市場驅動力將是高密度封裝及縮小封裝體積的需求;而中長期則是低成本及高效能的需求。目前TSV製作成本仍高,藉由降低填孔及接合製程的成本,就能大幅降低整個TSV的製作成本,而在2010年利用3D IC技術可望與打線封裝之成本相抗衡,在堆疊八層以上後,打線封裝的良率降低、封裝體積變厚都將使得3D IC技術優勢更加的突顯。可攜式電子產品要求功能越來越多,效能越來越好,也需要倍增的記憶容量,因此3D IC技術目前相當受到重視,最終勢必也將逐漸普及,並將以異質晶片整合的優勢帶給電子產業不小的衝擊。

(本文作者任職於工研院電光所)

| 參考文獻 |

| 1.M. Umemoto, et al, “High-Performance Vertical Interconnection for high-density 3D Chip Stacking Package,” Proc. 54th Electronic Components and Technology Conf, May 2004, pp. 616-623 2.P. Ramm, et al, “Three dimensional metallization for vertically integrated circuits,” Microelectronic Engineering, Vol. 37-38 (1997), pp. 39-47. 3.W. C. Lo, et al., “3D Chip-to-Chip Stacking with Through Silicon Interconnec,” Internationa VLSI Technology Technology, Systems and Applications, April 2007, pp. 72-73. 4.W. C. Lo, et al., “An Innovative Chip-to-Wafer and Wafer-to-Wafer Stacking,” Proc. 56th Electronic Components and Technology Conf, May 2006, pp. 337-342. 5.”Wafer Bonding Using Microwave Heating2f Parylene for MEMS Packaging”, Electronic Components and Technology Conference, 2004 6.”Morphology and Bond Strength of Copper Wafer Bonding”, Electrochemical and Solid-State Letters, 2004 7.”Diffusion Bonding of Gold”, Gold Bulletin, 1998 8.”Strong, high-yield and low-temperature thermocompression silicon wafer-level bonding with gold”, IOP Publishing Ltd, 2004 9.”Ultra-high-density 3D Chip Stacking Technology”, Electronic Components and Technology Conference, 2004 10.”Low-temperature silicon wafer-to-wafer bonding using gold at eutectic temperature” 11.”Reliability Study of Wafer Bonding for Micro-Electro-Mechanical Systems” 12.Sematech, “3D Interconnects and the ITRS Roadmap”, 3D Architectures for Semiconductor Integration and Packaging, 2005. 13.EV Group, “ Manufacturing Solutions for Wafer-to-Wafer and Chip-to-Wafer 3D Integration Schemes”, 3D Architectures for Semiconductor Integration and Packaging, 2006. 14.Yole Developpement, “3D IC & TSV Packaging:Market drivers, Cost, Technologies & Forecasts”, ITRI – 3D TSV Workshop, March 2008. 15.CEA-Leti, “CEA-Leti 3D Activities and Roadmap”, EMC-3D, 2007. 16.C.S. Tan, “Wafer Level Three-Dimensional (3-D) Integration”, ITRI, 2008 |