矽光子與共同封裝光學被視為AI算力救星,但第一線工程師面對的是良率如賭博的現實。從光損可視化到電光整合設計,這場量產攻堅戰的本質,是一場工業級的視力校正工程。

當我們談論矽光子(Silicon Photonics)或共同封裝光學(CPO)時,多數人的目光總是被那些亮眼的數據吸引:功耗降低七成、頻寬翻倍、解決AI算力的「功耗牆」。但這些漂亮的概念背後,隱藏著一個極其殘酷的現實——這項技術在量產線上的良率表現,目前更像是一場賭博,而非成熟的工業流程。

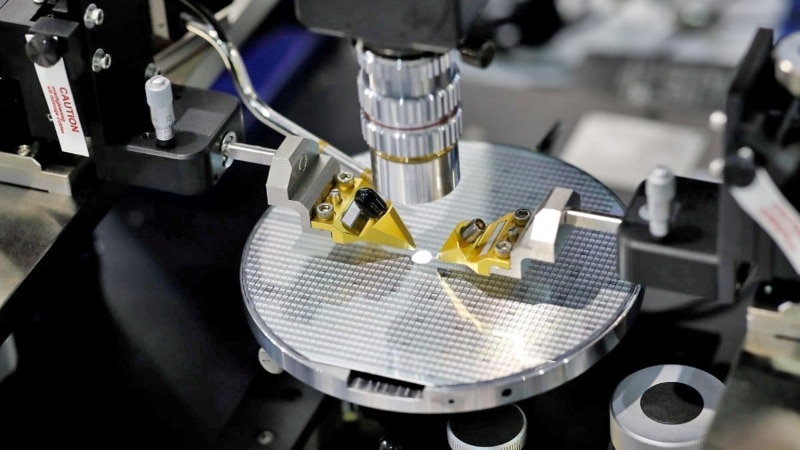

不只是各家廠商在設計與製造,甚至測試時都沒有標準可依循,核心問題在於「黑箱作業」。在傳統半導體電路中,訊號品質用電子顯微鏡或探針測一下就知道,但在光的世界裡,光子積體電路(PIC)的測試比瞎子摸象還誇張。

良率如賭博 透視技術破解光損

過去的PIC測試多半只能量測輸入與輸出的光損數值,就像買了一個濾水器,發現出來的水變少了,你只知道「水漏掉了」,卻完全不知道是濾芯破了還是水管裂了。這種「知其然不知其所以然」的測試困局,導致除錯時間長得嚇人,良率收斂極慢。在800G邁向3.2T的軍備競賽中,這種「瞎子摸象」的研發模式已經成為阻礙商業化的頭號殺手。

為了解決這個黑箱問題,宜特與光焱科技(EnliTech)深度結盟推出的NightJar光學檢測平台,本質上就是給研發人員一副「透視眼鏡」。它利用高光譜成像技術,捕捉光在晶片內因缺陷產生的微弱散射,讓原本不可見的光損直接「可視化」。

當工程師能直接看到光在哪裡洩漏,就能將這些數據與設計布局(Layout)強行對齊,找出到底是導光模態外洩,還是製程中的微小瑕疵。這不是單純的檢測,而是讓客戶能拿到「鐵證」,去校準製程參數,將NRE(一次性工程費用)降到最低。

不可重工時代 一顆壞就全盤報廢

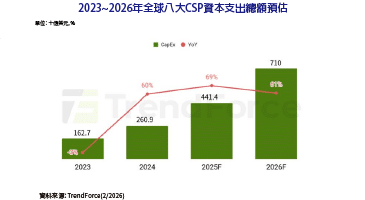

這項技術的商業意義極其巨大。NVIDIA預計在2027年推出的Rubin Ultra平台,將全面導入CPO技術。這種將光引擎直接封裝在晶片旁的「體內手術」,具備一個致命傷:不可重工(Non-reworkable)。

這是一個極其恐怖的商務邏輯。在Rubin世代的NVL72機櫃中,一個NVSwitch托盤上封裝了6顆交換晶片與數十顆光引擎,只要其中一顆在出廠測試時壞了,或是光纖對準歪了區區1微米,整片造價數十萬美金的板子就得直接報廢。

你不能像修手機一樣拆下來換個零件。在這種「一顆壞、全盤輸」的極致壓力下,如果沒有強大的量測與預警技術支撐,量產成本將會高到讓任何巨頭都感到窒息。

電光設計斷層 封裝廠接不住設計圖

除了「看見問題」,另一個量產鴻溝在於設計與製造的斷層。恩萊特科技總經理蘇正宇觀察到,矽光子難產的另一個主因是電子設計自動化(EDA)與光學設計之間的脫節。過去電歸電、光歸光,兩套系統互不相干。

但到了CPO世代,電訊號與光訊號在極小空間內高度整合,如果沒有像恩萊特推出的電光整合EPDA方案,工程師畫出來的設計圖,封裝廠根本接不住。

恩萊特透過串聯Siemens EDA工具與自研光學軟體,填補了這道空白,確保設計初期就能考慮到後續封裝的訊號完整性與散熱挑戰。

產能重心轉移中 台灣站穩執刀者位置

在美國PIC Summit USA的現場,充滿了技術領先的北美新創(如Ayar Labs或LightMatter)的集體焦慮。他們擁有頂尖的演算法與設計,卻發現若得不到台灣晶圓代工廠與封測廠(OSAT)的支持,量產僅是空談。

這種「把研發搬到產能旁邊」的現象,正是因為台灣具備了從工研院的驗證平台、宜特的精密量測,到恩萊特的電光整合軟體等完整的「執刀」能力。

2027到2028年將是初步產品量產的合理節點。這並非研發進度落後,而是產業正在進行理性的評估與「世代延續性」的鋪路。當銅線傳輸在物理極限前撞牆,矽光子的經濟效益才會顯現。

矽光子已經不再只是物理實驗室裡的波長與頻率問題,它變成了一場整合競賽。