在進行相關閱讀之前,讀者務必了解一些名詞的定義。如邏輯分析儀(Logic Analyzer)為可量測隨著時間而變化電壓的儀器。相較於傳統示波器顯示連續性電壓值變化,邏輯分析儀分別顯示「高」與「低」兩值的電壓,且它的輸入頻道數比示波器多,一般最少有8個頻道,多者超過100個頻道。在一般情況下,一個頻道相當於1位元。圖案產生器(Pattern Generator)則屬於訊號產生儀的一種,它可以產生數位訊號且輸出頻道數也非常多,能以一定周期改變相對頻道的圖案,同時一邊進行輸出動作。

邏輯分析儀/圖案產生器結構複雜

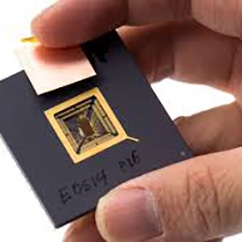

由USB邏輯分析儀與圖案產生器電路基板(圖1)的實際外觀可知,電路的導線與扁平封裝元件較多,因此較為複雜。

不過,在這些主要功能中,由於從被測對象中擷取訊號需要較強大的需求,因而委託複雜可程式邏輯裝置(CPLD)進行處理;至於轉送從靜態隨機存取記憶體 (SRAM)下載來的訊號、以及下載至個人電腦所需的指令解讀作業,則由個人網際網路通訊器(PIC)以較低速進行處理;至於發現觸發模式的工作,則由 PIC與CPLD共同處理。

圖案產生器的主要功能為高速產生8位元的訊號、解讀個人電腦傳來的指令,以變更圖案產生方法。分別由CPLD與PIC進行處理。由於PIC16F877A並無USB通訊功能,因此其與個人電腦間須設置USB平行轉換晶片FT245BM當作介面。

從主要元件結構來看,圖1的外形尺寸為150毫米×100毫米雙面電路板,上方並設有CPLD電路板;至於CPLD介面則使用EPM240T100C5晶片,組裝在CPLD電路板上;PIC使用PIC16F877A,並利用晶片插座的插拔方式進行PIC程式的輸入程式化作業;而USB的介面則使用 FT245BM。

值得一提的是,USB與電腦的通訊都利用圖1左側的USB連接器進行,在其他元件部分,靜態隨機存取記憶體使用CY7C1021BV33-10ZI;比較器(Regulator)使用TA48M033S,其屬於低降下類型(Drop Type)3.3伏特輸出,可供給CPLD電源。時脈器使用FXO-37F,屬於表面封裝型50MHz石英振盪器,CPLD根據此時脈器動作,因此邏輯分析儀的時序速度與圖案產生器的圖案產生速度同樣是50MHz。

保險絲使用可復原式保險絲REX025,該保險絲即使在高溫融斷時,待溫度降低就能夠恢復原狀,因此不需任何更換作業。尤其是使用USB電源驅動電路時,建議盡量使用可復原式保險絲,避免實際應用電流超過500毫安培。

邏輯分析儀與圖案產生器的輸入端同樣都設有8個探針,CPLD基板設有25接腳的母連接器,其可利用公-公直線平行纜線(Straight Parallel Cable)進行CPLD程式作業,此外,CPLD基板還設有10接腳座,可利用下載纜線ByteBlaster進行CPLD程式作業。圖2是硬體方塊圖,圖3~圖8是各單元的電路圖。

從CPLD EPM240T100C5(MAXⅡ)的周邊電路圖(圖3)可知,圖中50MHz石英振盪器與3.3伏特比較器須以銲接方式固定在電路基板上,CPLD的程式化作業則利用D sub 25接腳母連接器或10接腳的座進行。

若無CPLD電路基板時,必須將CPLD電路基板銲接於本周邊電路基板上,此時無D sub 25接腳連接器,就只能利用ByteBlaster進行程式化作業。

微處理器PIC16F877A的周邊電路利用本電路控制硬體系統(圖4)。圖4的USB匯流排連接至FT245BM,可與電腦進行資料相互傳輸,若連接至複雜可程式邏輯裝置,則能與複雜可程式邏輯裝置進行資料相互傳輸。在時脈方面則使用20MHz陶瓷振盪器與+5伏特電源。

圖5是USB介面FT245BM周邊電路圖,利用該電路的連接進行USB平行轉換。該晶片會將USB連接器的端子輸入資料當作平行資料(Parallel Data)輸出至RD0~RD7;反之,則可將輸入至RD0~RD7的平行資料當做序號,輸出至USB連接器的D+,D-端子。

FT245BM的時脈器使用20MHz陶瓷振盪器,電源為+5伏特。USB連接器使用基板組裝用B型母連接器,其中端子被當作本電路板+5伏特電源使用。

圖6則是靜態隨機存取記憶體CY7C1021B V33-10Z1的周邊電路圖,靜態隨機存取記憶體的位元寬度為16位元,位址空間為64K。

由於此周邊電路並未完全使用靜態隨機存取記憶體的位址空間,僅使用8位元的位元寬度與4K的位址空間,因此8位元的資料與12位元的位址空間連接至 CPLD時,DUT的8位元資料會透過CPLD將4096個資料寫入靜態隨機存取記憶體,反之,則從靜態隨機存取記憶體讀取的資料,再透過CPLD轉送至 PIC。靜態隨機存取記憶體多餘端子包括8位元的資料與4位元的位址空間未來可作擴充用,同時可對13接腳連接器進行資料輸出。

靜態隨機存取記憶體的讀、寫、晶片設定、輸出設定皆透過CPLD控制。此靜態隨機存取記憶體的讀、寫只需10奈秒,因此可達最高頻率100MHz的資料讀取、寫入。此外,該電路的寫入頻率為50MHz、讀取頻率為100MHz、以及使用+3.3伏特電源。

連接邏輯分析儀探針的連接器與連接圖案產生器的連接器的連接方法(圖7),事實上直接用銲接方式將探針、端子固定,或是使用連接器都可以達到預期效果。

圖9是CPLD電路基板連接器的連接方法,須配合CPLD電路基板(圖8)的連接器孔穴尺寸、位置,進行布線與元件設置(Layout)。

CPLD的主要功能有三項分別為從DUT高速擷取8位元的訊號轉送至靜態隨機存取記憶體、高速產生8位元的訊號並輸入、發現觸發模式。

亦即由複雜可程式邏輯裝置並聯高速進行以上工作,若這些工作全部委託類似PIC微處理器處理顯然不妥,因此皆交由CPLD進行處理。

圖9是CPLD內部電路的時脈結構,圖中的靜態隨機存取記憶體控制器主要功能是控制靜態隨機存取記憶體的讀寫動作,DUT的8位元資料與50MHz同步寫入靜態隨機存取記憶體,由於時脈的一個行程須寫入8位元,因此邏輯分析儀的頻道數為8個頻道,時序速度變成50MHz。

靜態隨機存取記憶體的寫入由CPLD進行主導,讀取則由PIC進行,PIC一邊監控從CPLD的「備妥讀取」,在一旦變成可讀取狀態時,輸出頻閃觀測器 (Strobe),便立即讀取靜態隨機存取記憶體的資料;換言之,讀取速度與從PIC的讀取Strobe頻率相同時,會轉變為比較低速的狀態,大約在 100kHz左右。

觸發控制器會不斷與DUT資料、觸發模式進行比較,並將一致的資訊傳給靜態隨機存取記憶體控制器。

產生儀(Generator)控制器會產生8位元的圖案輸出,產生儀控制器的頻道數為8個,圖案更新速度變成50MHz。

電阻控制器內部有8位元的電阻可利用PIC改寫,此外,電阻值會傳送到其他模組。

複雜可程式邏輯裝置的內部電路呈現雙層結構狀,CPLD頂端為上層結構,該模組的輸出、入同時也是CPLD的輸出、入。

PIC為電路基板控制功臣

控制用的微電腦使用PIC16F877A晶片,為PIC16F877的改良版,兩者主要差異是基準電壓值與比較儀(Comparator)。

雖然PIC可直接進行基板程式化(On Keyboard Programming),不過此電路基板設有晶片插座,程式化作業時須先將PIC從晶片插座拔除,PIC寫入器才可寫入程式。

PIC16F877A的額定電源電壓為4.0~5.5伏特,可直接使用USB的+5伏特端子,該端子的最大容許電流為500毫安培,基於安全考量,可使用上述介紹的可復原式保險絲。

USB邏輯分析儀與圖案產生器的主要構成分別是電腦、PIC與CPLD,其中電腦與CPLD的相容性不佳,無法直接傳輸資料,因此PIC成為電腦與CPLD兩者介面,此外,PIC還兼具整體電路基板的控制。

在執行具體作業步驟前,首先解讀電腦指令控制CPLD的模式,最初,將CPLD傳來的資料與電腦作同步傳輸,換言之,CPLD主要工作就是「大量、簡易、高速」,PIC主要工作是「複雜、少量、低速」。

由於PIC16F877A無通訊模組無法直接與USB的連接器連接,因此必須透過FT245BM與電腦進行通訊,FT245BM具備384位元先進先出 (First-In First-Out, FIFO)緩衝器,不過無法保存超過該容量的資料,因此特別設定所謂的「口袋(Pocket)」單位,每個口袋定義為256位元組。

目標是將一個口袋的資料置留在先進先出緩衝器內,接著主機讀取一個口袋的資料,立即清空先進先出緩衝器,上述作業反覆16次將16×256=4,096位元組的資料從目標轉送至主機,最後結束一連串的下載作業。

圖10是4096位元組資料從DUT下載至電腦的流動路徑,具體作業步驟如下:

視窗的應用操作技巧

邏輯分析儀與圖案產生器的USB介面使用FT245BM,使用前須作模組驅動器的安裝(Device Driver Install)作業,具體方法使用USB監控(UsbLogMon)的EXE檔案與Visual C++ Project進行邏輯安裝作業。

由於本USB邏輯分析儀具備圖案產生器功能,因此可以將它當作DUT使用。如圖1所示邏輯分析儀的8頻道探針連接於圖案產生器。

上述安裝作業完成後,利用USB連接器將硬體與個人電腦連接,在EXE Director有UsbLogMon.exe,只要點選兩下就能夠啟動圖13的視窗的應用。

接著壓下「運轉(Run)」鍵,原始設定為256進位輸出的8頻道圖案產生器,可以用邏輯分析儀監控(圖14)。不過由於此處該狀態並未施加觸發,因此壓下「Run」鍵時波形的位置會朝左右移動,這意味著該狀態並不是「觸發模式」而是「內同步模式(Free Run Mode)」。

圖14畫面右下方出現「觸發模式」確認盒(Check Box),因此在確認後再度按下「Run」按鍵,此時波形左側的8個頻道始終變成「0」,數次按下「Run」按鍵結果一樣,即以00000000施加觸發。

寫著「觸發(7:0)」的編輯盒內部有00000000,它是指觸發圖案(Trigger Patten),接著將它當作00000000按下「Run」按鍵就變成圖15的畫面。

由圖15可知波形是從該值產生,事實上8位元是CPLD的阻抗值,它從電腦通過USB介面傳送到PIC,PIC再將CPLD的阻抗值觸發(7:0)改成此值獲得的結果。

圖14畫面左側出現「觸發(7:0)」的編輯盒,它同樣是CPLD的阻抗值,如果變更該值觸發的位置會變動,如變更成「01」時,圖16的觸發(10000000)位置會朝左右變動,由此可知利用上述操作技巧,可以觀察施加觸發的資料。假設該值變更成「10」時,觸發位置會朝右方變動,變更成「11」時觸發位置會朝更右方變動。

圖14畫面最右出現「一般時期(Genperiod)(7:0)」的編輯盒內部有「11111111」,表示圖案產生器的周期。雖然是「11111111」,不過CPLD內部的計數器一旦進入256,立即折返變成0,亦即256計數進位,假設使用者欲作201進位時,必需將該值設定成「11001000」,其結果如圖17所示,周期變成201行程(Cycle)。

圖案產生器採雙模式運作

圖案產生器有兩種模式,分別是原始設定的計數模式、脈衝模式。

此處將「基因型(Gentype)」的編輯盒設定成「1」,其他則依照圖18的畫面,如此一來就會出現脈衝波模式的波形,而在脈衝波的周期最上方,亦即最高階位元時最長,高達65,536個行程,越往下方周期變成一半。此外脈衝寬度「高」的狀態也可用「一般時期(7:0)」變更。

利用旋轉(Spin)按鍵將時間軸的尺度設定成最小時,就會變成圖19的模樣,因此,圖19是改變時間軸方向的解析度,類似這樣的時序速度,亦即時間軸方向的解析度與邏輯分析儀、圖案產生器受到CPLD的50MHz影響下,動作速度皆為20奈秒。

以上介紹USB用邏輯分析儀與圖案產生器的製作技巧與動作特性,一般認為USB裝置的普及化下,類似邏輯分析儀與圖案產生器在研發階段扮演的角色也將會漸形重要。