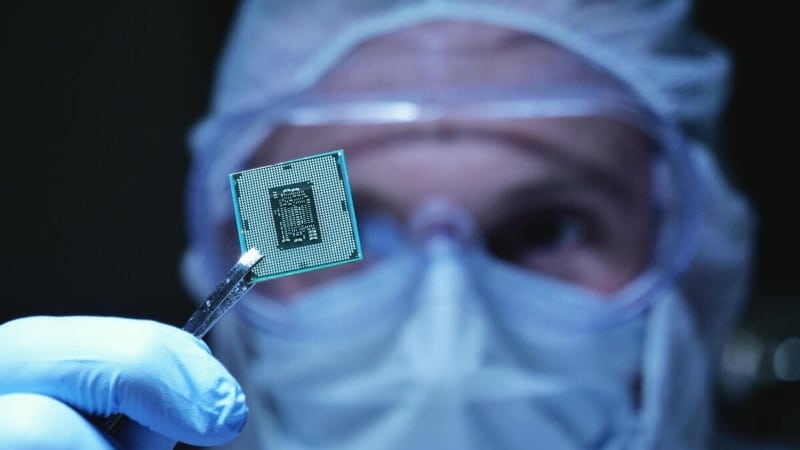

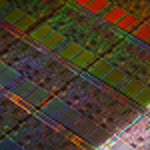

3D封裝技術再現新突破。三星(Samsung)近日宣布,該公司已經開發出業界首個12層三維矽穿孔(3D-TSV)封裝技術。3D-TSV技術(尤其是12層)被認為是現今大規模量產高性能晶片所面臨的巨大挑戰之一,因為需要極高的精度才能通過擁有60,000多個TSV孔、以3D封裝垂直互聯的12個DRAM晶片。

三星電子測試與系統封裝執行副總裁Hong-Joo Baek表示,隨著各種新時代的應用不斷興起,像是人工智慧(AI)、高性能運算(HPC)等,能提升記憶體性能的封裝技術變得越來越重要,也越來越複雜。同時,隨著摩爾定律的擴展逐漸達到極限,預計3D-TSV技術的效用在未來將更加重要與關鍵,而該公司希望在此一領域一直維持在領先地位。

據悉,12層3D-TSV封裝技術的厚度與當前8層第二代高頻寬顯示記憶體(HBM2)相同,這在元件設計上是一大進步,因對客戶而言意味著可行更高容量、更高性能的設計,而毋須大幅改變系統架構設計。此外,透過3D封裝技術,將可使晶片間的資料傳輸時間更明顯的縮短,在明顯提高資料傳輸速度的也降低功率損耗。

總而言之,依靠新研發的12層3D-TSV 技術,三星將可為資料密集、高速傳輸等應用提供效能更高的DRAM;而且,透過將堆疊層數從8個增加至12個,三星將能在很短的時間內大量生產24GB高頻寬記憶體(容量為目前是市場上8GB高頻記憶體的3倍)。另一方面,三星也希望憑藉12層3D-TSV技術,滿足快速成長的大容量HBM市場需求,並同時希望該公司在高階半導體/記憶體市場的競爭優勢。