光耦合器隔離功能發威 SPI /CAN匯流排資料不漏失

不過,加入一個額外零組件到串列資料通道上也會影響資料的吞吐量。這篇文章將討論SPI/CAN通訊協定的位元時序,深入探討有關資料位元率與光耦合器傳遞延遲時間的相關性,並提供實際的計算範例來協助設計工程師針對特定的匯流排資料傳輸率進行光耦合器效能的最佳化。

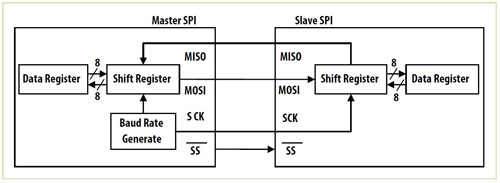

SPI匯流排/光耦合器運作分析

SPI匯流排提供了一個四線式的同步串列通訊介面,通常應用於微控制器(MCU)與周邊設備間,這四個連線訊號分別為主控輸入/從屬輸出(Master Input/Slave Output, MISO)、主控輸出/從屬輸入(Master Output/Slave Input, MOSI)、串列時脈(Serial Clock, SCK)以及從屬選擇或晶片選擇(Slave Select/Chip Select, SS)。

SPI系統中的主要控制元素為SPI資料暫存器(Data Register),實際上有兩個8位元資料暫存器,一個位於主控端,另一個則位於從屬端,兩者的組合共同形成了由MISO與MOSI兩個接腳所連接的16位元暫存器(圖1)。

|

| 圖1 SPI主控與從屬設備中的8位元資料暫存器,透過MISO與MOSI訊號連接形成16位元控制暫存器。 |

只有主控SPI模組可以啟動資料傳輸。傳輸動作由主控處理器將資料寫入主控資料暫存器開始,如果移位暫存器(Shift Register)為空,那麼位元組會立即傳送到移位暫存器並在串列時脈的控制下由MOSI接腳送出。

只有主控SPI模組可以產生串時脈訊號並使資料通訊與從屬設備同步,主控SPI通常將SS接腳設定為從屬選擇輸出,在資料傳輸進行前,SS接腳必須轉變為低電位並維持在該狀態直到整個傳輸動作完成;如果SS接腳變成高電位,那麼SPI連接埠會被強制進入靜止狀態(Idle State)。

有兩種SPI連線方式可以包含一個主控端與多個從屬端,分別為雛菊鏈鍵串接從屬設備以及並列連接從屬設備。被選用的從屬設備也可以透過多重主控通訊協定與多個主控端搭配運作,由於多個從屬設備的時脈順序與單一從屬端連接方式非常相似,因此本篇文章只介紹單一主控端與從屬端的連接方式。

有時候SPI連接埠只使用三條連接線進行通訊,主要是在周邊設備為固定組態時,例如在只可送出資料的狀況下降低輸入訊號的需求,或者是在只輸入資料時節省資料輸出訊號。

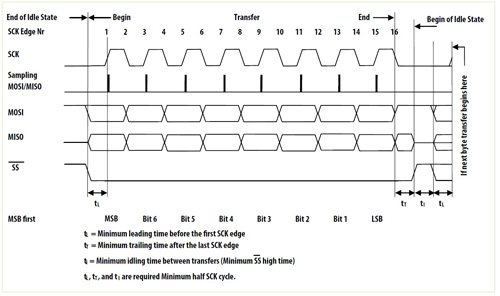

圖2中的SPI時序圖描述了SPI連接埠的控制設定,例如時脈為高電位啟動(CPOL=0)、在時脈奇數邊緣進行資料取樣(CPHA=0)、資料以MSB優先(LSBFE=0)方式傳輸等,對主控資料暫存器的讀寫動作會啟動資料傳輸運作,在典型的SPI資料傳輸過程中,會在SS成為低電位後的半個時間週期內發出第一時脈邊緣。SCK連線的第一個邊緣可以將主控移位暫存器的第一個資料位元透過MOSI移入從屬端,並在同時將從屬端的第一個資料位元透過MISO移入主控端。

|

| 圖2 在這個時脈圖中,主控SPI連接埠的資料會從串列時脈訊號的前緣移入從屬設備SPI連接埠,而從屬設備SPI連接埠提供的資料則會同時移入主控SPI連接埠,請參考圖中的MOSI與MISO接腳。 |

當SCK連線上的第二個邊緣發生時,先前鎖住的資料會移入移位暫存器的MSB位元,相同的動作會一再於SCK訊號的十六個邊緣重覆,直到主控端中所有八個資料位元移入從屬端且從屬端中的八個資料位元移入主控端為止,在最後一個位元移入後,資料便可以由移位暫存器傳送到並列的SPI資料暫存器。

在最後一個時脈邊緣後會出現一個發生於時脈訊號位準回到高電位前,最小半個時脈週期的尾隨時間tT,接著SPI開始進入下個靜止狀態,SS訊號連接線會維持在高電位狀態最少半個時脈的靜止時間tI,才可使時脈位準再次成為低電位狀態。

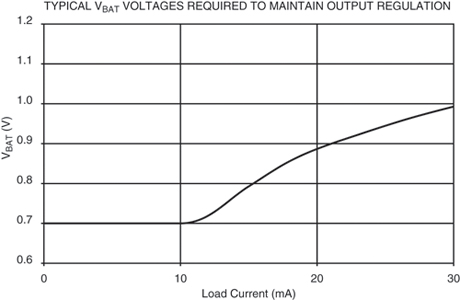

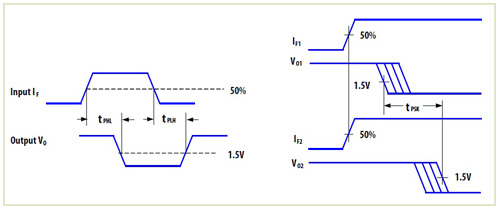

在將光耦合器加入SPI介面之前,先來分析訊號通過光耦合器時,光耦合器傳遞延遲時間與資料傳輸率間的關係。光耦合器的最大高電位到低電位(tPHL)與低電位到高電位(tPLH)傳遞延遲時間將決定元件的最高資料傳輸率(圖3)。最大傳遞延遲tP(MAX)為tPH與tPLH兩者中較大者,光耦合器在傳輸不歸零編碼(Non Return to Zero, NRZ)資料時需要資料位元時間長度τ最小要大於tP(MAX),也就是τ≧TP(MAX),因此最高資料傳輸率為:

|

| 圖3 光耦合器的傳遞延遲時間偏離由最低與最高傳遞延遲時間之間的差異決定。 |

對於使用歸零編碼(Return to Zero, RZ)資料的時脈訊號,時脈週期包含了高電位與低電位時間(τ=tHIGH+tLOW),對於傳送50%有效週期率時脈訊號的光耦合器,則要求半個時脈週期必須大於tP(MAX),也就是τ/2≧TP(MAX),因此最高時脈頻率可以透過以下方程式決定:

當資料通過並列訊號線同步傳送時,光電耦合器的傳遞延遲偏離tPSK就成為可能決定最高並列資料傳輸率的重要因素。如果並列資料透過兩個獨立的光耦合器或一個多通道光耦合器傳送,那麼各個通道間不同的傳遞延遲時間將造成資料透過光耦合器輸出的時間相異;如果這個傳遞延遲的時間過大,那麼就會限制並列資料透過光耦合器傳送的最高速率。

由圖3可以看到,傳遞延遲時間偏離定義為相同驅動電流、電壓、輸出負載以及工作溫度等相同條件下,各光耦合器通道最低與最高傳遞延遲時間之間的差異。光耦合器的tPSK會在資料與訊號線上形成不確定狀態,通常來說,可以透過並列光耦合器傳送的絕對最小脈衝寬度為兩倍的tPSK,也就是TPW≧2tPSK,因此最高資料傳輸率為:

較為保守且安全的設計,應該是使用較長的脈衝寬度,以確保電路中其他部分造成的所有額外不確定性不會帶來任何問題。

SPI系統設計實例

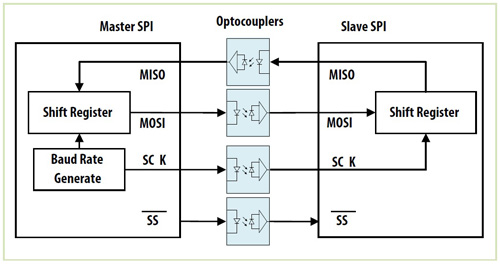

圖4顯示出典型的四接線SPI隔離介面,其中每個MISO或MOSI接線都採用單通道或單一光耦合器來提供主控端與從屬端間的電氣隔離。

|

| 圖4 Avago的ACPL-M72T單通道光耦合器可以隔離主控端與從屬端SPI設備間所有的訊號路徑。 |

舉例來說,若使用安華高(Avago)的光耦合器ACPL-M72T來提供MISO、MOSI與SCK等訊號連線的隔離功能,由光耦合器中的產品規格書中就可看出,tP(MAX)為100奈秒(ns)且最高tPSK為60ns,將這些數值代入先前的方程式就可得到最高的SPI資料傳輸率。

以下的計算提供了使用ACPL-M72T光耦合器切換規格做為SPI資料時脈程序的參考設計範例。由於SPI時脈採用NZ編碼方式,因此先將方程式(2)代入SCK,接著計算最時脈頻率:

由於主控端設備會以並列且同步的方式送出MOSI與SCK訊號,因此必須接著將方程式(3)代入這兩條連接線來決定在可能訊號變化率發生條件下的MOSI最高資料傳輸率:

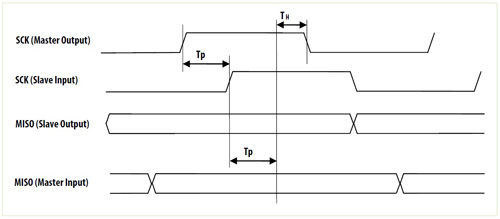

MISO與時脈訊號間的同步方式和MOSI不同。當時脈訊號由主控端傳送到從屬端時,光耦合器會在SCK上造成傳遞延遲偏離,在從屬端收到時脈訊號後,從屬端輸出資料到主控端路徑上的光耦合器也會在MISO上造成傳遞延遲偏離,主控端必須在相同時脈訊號的第二個邊緣變化前對資料進行取樣,因而傳遞延遲時間的兩倍必須低於時脈時間的一半,也就是2tP(MAX)≦τ/2,MISO的最高資料傳輸率為(圖5):

|

| 圖5 SCK與MISO訊號的時序必須考慮到整個路徑的來回傳遞延遲,以決定MISO訊號路徑上的最高資料傳輸率。 |

最後,在決定最低資料傳輸率後,就可以使用這個傳輸率在所有的計算上,比較fSCK、DRMOSI與DRMISO等三個資料傳輸率,最低資料傳輸率為MISO連線的2.5MBd,因此相對應的時脈頻率應該設定為2.5MHz,這是資料傳輸不會發生任何漏失位元的安全限制。較為保守的方式是將時脈頻率設定進一步降低到大約2MHz,而非計算取得的2.5MHz,以確保在其他額外非確定性因素影響下資料的完整性。

在資料傳輸時,SS連接線通常擁有較長的靜止時間tI,因此可以使用較低速的光耦合器,如tI設定為高於1微秒(μs),那麼就可採用ACPL-K49T。

表1列出了各種不同SPI時脈頻率下的光耦合器最高資料傳輸率與最大傳遞延遲要求,設計人員可依此做為挑選光耦合器的參考。

|

CAN應用分析與設計實例

CAN應用分析與設計實例

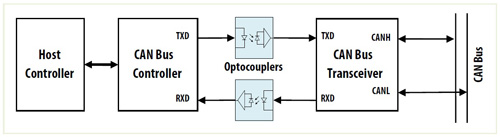

接下來討論CAN匯流排。CAN匯流排是一個傳輸NRZ編碼串列非同步訊息的兩線式資料匯流排,典型的節點連接方式包含一個主控端控制器、一個CAN匯流排控制器以及一個匯流排收發器(圖6)。

|

| 圖6 在典型的CAN節點上,匯流排收發器使用CANH與CANL接腳將差動式訊號傳送到CAN匯流排上,資料能以任意方向傳送,光隔離元件則可以用來提供匯流排收發器與匯流排控制器間的電氣隔離。 |

兩線式CAN匯流排上的訊號為由匯流排收發器提供CANH與CANL訊號形成的差動式訊號,訊號接腳採雙向式設計,因此訊號可以由任意方向與匯流排控制器進行傳輸;除此之外,其他選擇的功能還包括可以連接到節點的接地連線GND,以及匯流排電壓感測V+訊號。

CAN匯流排收發器中的接收器電路會隨時透過CANH/CANL接腳監測匯流排上的差動式訊號,並將它轉換成為可以傳送給控制器的單端訊號流。

同樣地,當匯流排控制器要送出資料時,它的發射器電路會送出單端訊號流到匯流排收發器,接著再轉換為差動電壓並將訊號送到CAN匯流排上。

對需要隔離功能的CAN匯流排節點,光耦合器可被安排在CAN控制器與CAN匯流排收發器之間,因此可以提供控制器與匯流排以及其他CAN節點間的電氣隔離。

CAN匯流排訊息使用不同形態的訊框方式傳送,資料訊框(Data Frame)以訊框起始(Start of Frame)位元開頭並以訊框結束(End of Frame)位元做結。

訊框起始位元後的仲裁區(Arbitration Field)由11位元的辨識資訊(Identifier)開頭,訊息的辨識資訊描述了節點的優先次序以及資料形態,若有多個節點訊號於CAN匯流排上發生衝突時,即可依此做為依據,即時處理衝突狀況。

例如,擁有最高優先權限的訊息將成功傳送,使用較低權限訊息的節點可以在感應到這個情況時,自動停止傳送並維持在等待狀態。這樣的安排可以帶來CAN匯流排上無破壞性的仲裁控制,同時避免發生資料漏失的情況。

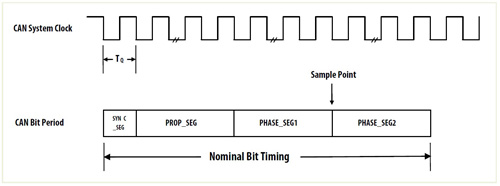

CAN的標稱位元時間(Nominal Bit Time, NBT)總共由四個部分所組成,分別為同步部分(SYNC_SEC)、傳遞延遲部分(PROP_SEG)、相位緩衝部分一(PHASE_SEG1)以及相位緩衝部分二(PHASE_SEG2)(圖7),組成公式如下所示:

|

| 圖7 CAN位元時間分為四個部份,分別為同步部份(SYNC_SEC)、傳遞延遲部份(PROP_SEG)、相位緩衝部份一(PHASE_SEG1)以及相位緩衝部份二(PHASE_SEG2)。 |

位元取樣點位於PHASE_SEG1的結束處,PHASE_SEG1與PHASE_SEG2的組合稱為取樣部分(Sample Segment)。

時間量TQ(Time Quantum)是一個由時脈振盪器或微控制器時脈取得的固定時間單位。另外,可控制預除器的時間預設由整數值1?32所構成,可以設定在目標值來產生所需的時間量:

其中fclock為振盪器時脈頻率,fCAN為CAN系統時脈頻率,m則為預除器設定值。

CAN位元時間以時間量為單位的倍數進行測量,CAN匯流排上單一標稱位元時間(NBT)的時間量可由最少8?25的數值控制。

同步部分固定為一個時間量,這個部分主要用來進行各個節點間的同步,每個CAN節點會將目前位元時間的SYN_SEG對齊到所傳送訊框起始位元的隱性邊緣。傳遞時間部分則可設定為1?8個時間量,並用來補償匯流排上的實體時間延遲。由發射節點A到接收節點B間的實際傳遞時間為:

上述式子中的tTX為節點A CAN控制器TXD到匯流排的傳輸傳遞時間延遲,包含了光耦合器與匯流排發射器的時間延遲;tBUS則為CAN匯流排纜線的傳遞時間延遲;而tRX為由匯流排到節點B CAN控制器RXD的接收傳遞時間延遲,包含匯流排接收器與光耦合器的時間延遲。

因此,設計人員可以確保位元數值正確取樣的傳遞延遲部分最小時間如下所示:

如果節點A與節點B擁有相同形態的收發器與光耦合器,那麼來回的傳遞延遲為:

PHASE_SEG1設定為1?8個TQ時間量長度,PHASE_SEG2通常等於PHASE_SEG1或是資訊處理時間(Information Processing Time, IPT)中較大者。不過當訊號經過重新同步以補償邊緣相位誤差時,PHASE_SEG1可被延長,而PHASE_SEG2可被縮短,PHASE_SEG1與PHASE_SEG2之間的調整會受到預先設定值的重新同步跳躍寬度(RJW)限制,最小RJW為一個TQ時間量,最大RJW則為四個TQ時間量,以及PHASE_SEG1時間量間的較小者。

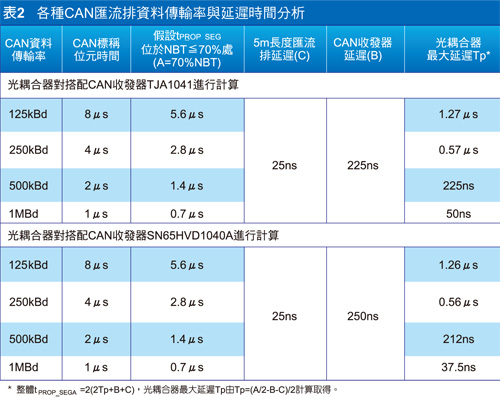

在決定CAN匯流排位元率後,設計師接著須計算位元時間量並檢查每部分的時間量需求。在其他匯流排通訊協定上,資料的取樣發生在位元時間的中心點,但在CAN通訊協定中,位元取樣會在PHASE_SEG1結尾與PHASE_SEG2開始時發生,依經驗值大約在位元時間80%位置。因此在選用CAN收發器與光耦合器時,設計師應將PROP_SEG限制在位元時間的70%處。表2列出各種CAN傳輸率選擇以及相關的匯流排特性與延遲時間。

|

要了解這些時序問題如何轉變成為真正的效能影響,可用兩個簡單的例子說明。

範例一

CAN匯流排系統標稱位元率為1Mbit/s,微控制器時脈頻率為20MHz,並選用具有如圖5所示功能的恩智浦(NXP)CAN收發器TJA1041以及安華高的光耦合器ACPL-M71T。

•步驟一

CAN標稱位元時間NBT=1/1Mbps=1000奈ns。將預除器設定為2可以得到CAN系統時脈為20MHz/2=10MHz,CAN時脈時間量TQ=1/10MHz=100ns。因此CAN標稱位元時間量即為NBT/TQ=1000ns/100ns=10。

•步驟二

由匯流排收發器與光耦合器的產品規格書中可以看出,發射與接收通道的最大傳遞延遲時間分別為250ns以及70ns。

假設匯流排傳遞延遲大約為5ns/m,那麼5公尺長的連線匯流排延遲為25ns,因此,CAN往返延遲時間就變成:

•步驟三

計算每個部分的時間量:

由步驟一中計算取得的時間量10,減去SYNC_SEG的1以及PROP_SEG的6,可以得到時間量3做為取樣部分。

因此將PHASE_SEG1設為時間量1且PHASE_SEG2設為時間量2,由於RJW為4與PHASE_SEG1的較低者,因此設為1,在這個情況下,取樣點位於(1+6+1)/10處,大約在位元時間的80%處(圖7)。

範例二

CAN匯流排系統標稱位元率為500kbps,微控制器時脈頻率為20MHz,並選用具有如圖5所示功能的恩智浦CAN收發器SN65HVD1040A以及安華高的光耦合器ACPL-M72T。

•步驟一

CAN標稱位元時間NBT=1/500kbit/s= 2000ns。將預除器設定為2可以得到CAN系統時脈為20MHz/2=10MHz,CAN時脈時間量TQ=1/10MHz=100ns。因此CAN標稱位元時間量的計算過程即為NBT/TQ=2000ns/100ns=20。

•步驟二

由匯流排收發器與光耦合器的產品規格書中可以看出,發射與接收通道的最大傳遞延遲時間分別為250ns以及200ns。

假設匯流排傳遞延遲大約為5ns/m,那麼5公尺長的連線匯流排延遲為25ns,因此,CAN往返延遲時間就變成:

•步驟三

計算每個部分的時間量:

由步驟一中計算取得的時間量20,減去SYNC_SEG的1以及PROP_SEG的9,可以得到時間量10做為取樣部分。因此將PHASE_SEG1設為時間量5且PHASE_SEG2設為時間量5,由於RJW為4與PHASE_SEG1的較低者,因此設為4,在這個情況下,取樣點位於(1+9+5)/20處,大約在位元時間的75%處。

因此,透過對SPI與CAN系統中訊號傳遞延遲的深入了解,設計人員可以選擇最適合的光耦合器來確保不會有資料漏失的情況發生,同時提供匯流排與控制器間的電氣隔離。