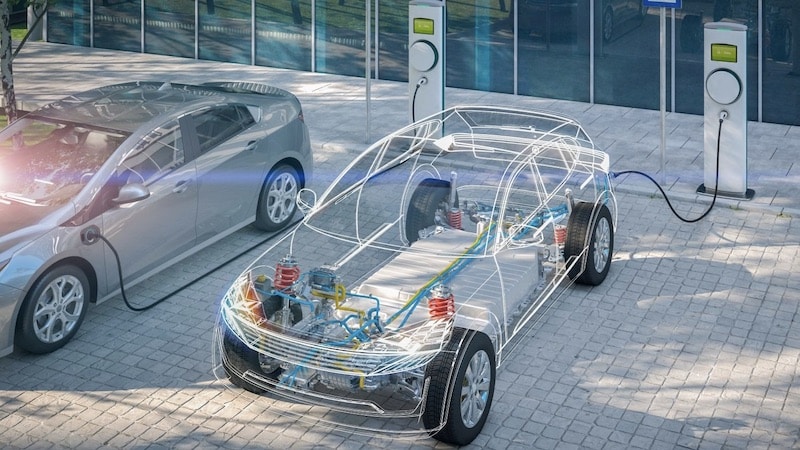

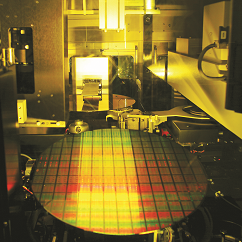

新思(Synopsys)與台積電合作實現系統整合,並因應高效能運算(HPC)應用所要求的效能、功耗和面積目標。這些方法在系統整合單晶片(TSMC-SoIC)技術中支援3D晶片堆疊,並在整合扇出型(InFO)和基板上晶圓上晶片(CoWoS)封裝技術中提供2.5/3D先進封裝的支援。且解決從探索到簽核完整流程所面臨的挑戰,進而實現能包含數千億個電晶體於單一封包的新一代超融合 3D系統。

台積電設計建構管理處副總經理Suk Lee表示,台積電與開放創新平台(OIP)的生態系合作夥伴密切合作,以推動HPC領域的下一波創新浪潮。此次合作結合了新思科技3DIC Compiler平台與台積電的晶片堆疊和先進的封裝技術,這將協助客戶滿足功耗和效能的設計要求,並成功設計出用於HPC應用的先進SoC。

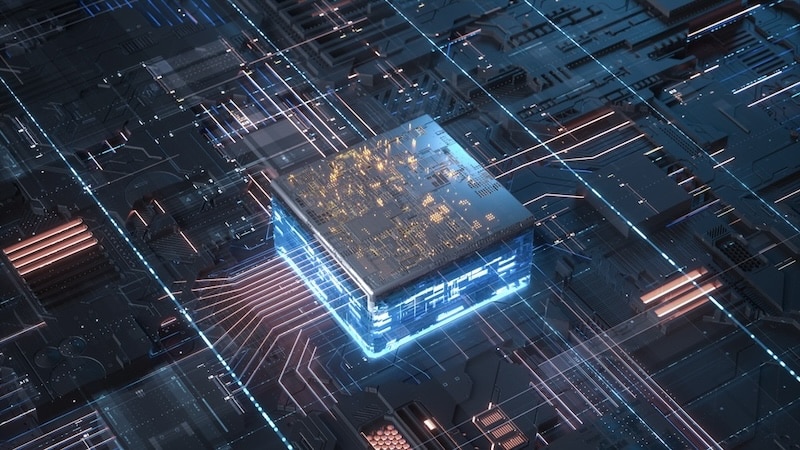

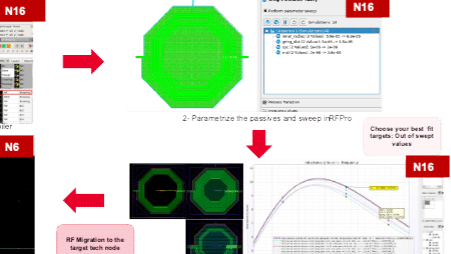

3DIC Compiler平台是一個完整的端到端解決方案,可用於實現高效率的2.5/3D多晶片設計和全系統整合。3DIC Compiler平台乃建立在「新思科計融合設計平台」(Synopsys Fusion Design Platform)單數據模型基礎架構上,結合了變革性的多晶片設計能力,並利用新思科技的實作和簽核技術,在單一整合的3DIC單座艙中,提供從探索到簽核的完整平台。該超融合解決方案包括2D和3D的視覺化、跨階層探索和規劃、設計與實作、測試設計以及全系統驗證和簽核分析。

新思科技矽晶實現事業群總經理Shankar Krishnamoorthy表示,若要達到實質的擴展以因應AI為主的工作負載和域優化運算的激增,則需仰賴創新的領導及以緊密的合作。利用3DIC Compiler平台和台積電易於取得的整合技術所帶來的效能、功耗和電晶體體積密度的提升,將有助於形塑各種現有和新興的應用與市場。