是德科技宣布與英特爾晶圓代工合作支援嵌入式多晶片互連橋接(EMIB-T)技術,此尖端創新技術旨在改善AI和資料中心市場的高效能封裝解決方案,並支援Intel 18A製程節點。

隨著AI與資料中心工作負載的複雜度持續增加,確保小晶片與3DIC之間的可靠通訊變得越來越關鍵。高速資料傳輸和高效率電源傳輸對於滿足次世代半導體應用的效能需求至關重要。半導體產業透過新興的開放式標準來解決這些挑戰,例如通用小晶片互連(UCIe)和Bunch of Wires(BoW)。這些標準為先進2.5D/3D或積層/有機封裝中的小晶片與3DIC定義互連通訊協定,實現不同設計平台之間的一致性及高品質的整合。

透過採用這些標準並驗證小晶片的相符性和鏈路餘量,是德科技EDA與英特爾晶圓代工為持續成長的小晶片互通性生態系統做出貢獻。這項合作旨在降低半導體設計的開發成本、減少風險並加速創新。

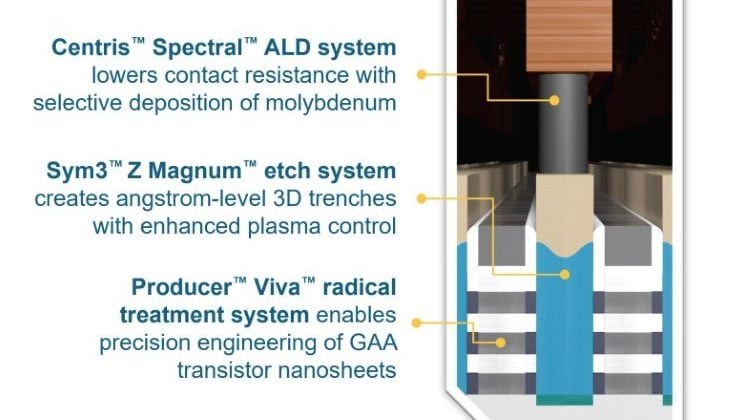

是德科技EDA的Chiplet PHY Designer是專為AI和資料中心應用量身打造的最新高速數位小晶片設計解決方案,現提供UCIe 2.0標準的進階模擬功能,並支援開放運算計畫BoW標準。作為一項先進的系統層級小晶片設計與晶粒間(D2D)設計解決方案,Chiplet PHY Designer可實現矽前層級驗證,進而簡化出貨下線流程。

英特爾晶圓代工生態系統技術辦公室副總裁暨總經理Suk Lee表示:「我們與是德科技EDA在EMIB-T矽橋技術的合作是推進高效能封裝解決方案的關鍵一步。透過整合UCIe 2.0等標準,我們為AI與資料中心應用提升小晶片設計的彈性,加速創新並確保客戶能精準地滿足次世代需求。」

是德科技設計工程軟體副總裁暨總經理Niels Faché表示:「是德科技EDA開創性的Chiplet PHY Designer持續重新定義矽前驗證,為小晶片設計師提供快速、精確的驗證能力。透過積極採用UCIe 2.0和BoW等不斷演進的標準,以及現在對英特爾晶圓代工EMIB-T的關鍵支援,我們正在使工程師能夠加速創新,並消除製造階段前昂貴的設計迭代。」