繼手機之後,智慧眼鏡、智慧手表等穿戴式裝置可望將系統耗電規格推向新的里程碑,因而也刺激小封裝、低功耗的現場可編程閘陣列(FPGA)導入需求,以扮演顯示器、I/O和相機子系統與主處理器之間的橋梁,協助分擔耗電量較高的處理器運算量,進而降低系統功耗。

萊迪思(Lattice)半導體台灣區總經理李泰成表示,相較於採用數千毫安時(mAh)鋰電池的手機,穿戴式裝置在系統空間限制下,大多僅能搭載600mAh以下容量的鋰電池,但卻要提供數日以上的續航力,導致系統業者為如何「省電」這件事傷透腦筋。由於業者發現時脈較高的主處理器對穿戴式裝置功耗影響甚鉅,因此開始擴大導入微控制器(MCU)或FPGA等協同處理器,以減少主處理器開啟的頻率。

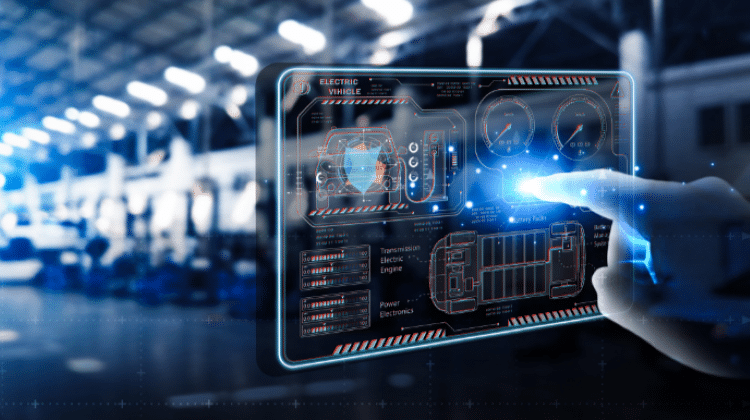

李泰成指出,基於協同處理器的設計概念,FPGA因具備大量平行運算及可編程特色,可應付顯示器、I/O和相機子系統等資料量較大的應用(圖4),相較於MCU更能突顯系統節能效益,正日益受到系統廠青睞。為進一步提高FPGA在穿戴式裝置市場的滲透率,萊迪思也積極耕耘更小型化的FPGA封裝技術,進而縮減晶片成本、耗能和占位空間。

另一方面,FPGA亦可藉由軟體編程功能,幫助系統廠快速實現所需的創新功能,毋須耗時打造高成本的特定應用積體電路(ASIC)。李泰成認為,對穿戴式裝置設計而言,FPGA不僅能推升系統電源效率,亦是加速新功能商用的推手,可望逐漸在市場上嶄露鋒芒。