你的高速產品在GHz時代是否能穩定運作?每一條線路都可能成為潛在風險。訊號延遲10皮秒、阻抗偏差1歐姆,都可能導致產品在量產前夕出現異常。透過訊號完整性與電源完整性模擬(Signal Integrity / Power Integrity Simulation, SIPI),可在設計階段識別潛在問題,讓高速產品順利量產。

在低速系統中,模擬或許只是輔助工具;但在高速設計下,任何訊號失真或雜訊都可能影響產品上市。SIPI模擬能在設計階段預測並修正問題,從眼圖、抖動到電源分配網路阻抗一次掌握。隨著訊號速率邁入GHz級(如PCIe Gen5/6、DDR5、USB4等),電氣問題可能導致資料錯誤、系統不穩,甚至無法上市。

最有效的預防方式,是在設計流程中導入SIPI模擬,預先找出潛在問題,提升設計成功率與可靠性。本文將介紹高速設計導入SIPI的十大關鍵,並分享實務導入流程,協助計更穩定、高效、具競爭力。

SIPI模擬原理概述

訊號完整性模擬是針對高速電路設計的預測性分析技術。透過準確建模與仿真工具,能在PCB尚未製作前預測訊號傳輸過程中的異常,並提早排除電氣風險。它可預測並消除訊號失真、干擾與反射;評估抖動(Jitter)、損耗、串音對系統穩定性的影響;確保訊號在高速環境下具可解碼性與一致性。

而電源完整性模擬則著重於電源分配網路(Power Distribution Network, PDN)的穩定性分析,確保電壓供應平穩並降低雜訊。它可預測電源平面雜訊、IR Drop與去耦電容配置效能,避免瞬態電壓波動影響系統運作。

在高速設計中,同步掌握SI與PI兩大核心面向,才能確保整體系統穩定性與可靠性。

高速設計導入SIPI關鍵考量

以下將透過各種關鍵考量,闡述SIPI模擬如何提升設計成功率。

高速訊號反射原因與阻抗控制

高速走線(Trace)、過孔(Via)或連接器(Connector)若阻抗不連續,訊號會反射回傳造成波形失真。透過SI模擬,可精確預測反射位置,並修正阻抗匹配,確保訊號穩定傳輸。

高速走線串音干擾

走線間距過小會產生電磁耦合,造成串音(Crosstalk),導致資料錯碼或位元錯誤率(Bit Error Rate, BER)增加。模擬可評估走線間距、層間影響,並建議使用防護走線或接地屏蔽,維持系統訊號完整度。

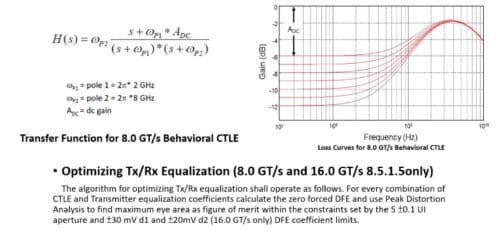

長距離訊號衰減與補償

高速訊號受導體損耗(Conductor Loss)與介質損耗(Dielectric Loss)影響,造成波形振幅衰減。SIPI模擬可協助設定走線寬度、材料,並評估通道補償技術(如Equalization、CTLE、DFE),確保訊號保持清晰。

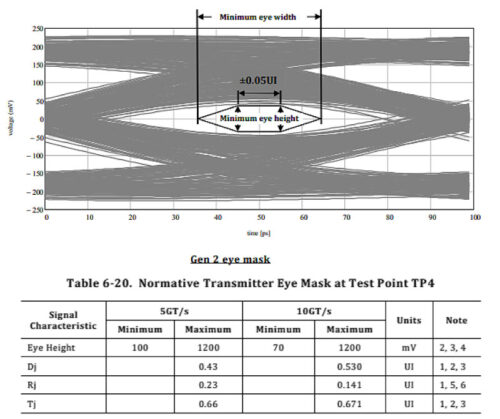

眼圖與時序分析

眼圖(Eye Diagram)可直觀評估訊號品質。透過模擬,能預測眼圖開口(Eye Height/Width)是否符合協定標準(如USB4、PCIe Gen5、DDR5),並縮短除錯週期(圖1)。

時序偏差(Skew)與抖動(Jitter)會影響時序容差(Setup/Hold Margin)。模擬可精確預測Delay、Skew、Jitter等參數,確保資料同步與眼圖對準。

差分訊號穩定性

差分訊號(Differential Signal)的對稱性與耦合性會影響其抗雜訊能力與穩定性。SI模擬可量化Skew、Common-mode Noise,確保差分對在極端條件下仍能穩定運作。

協定驗證與成本效益

透過模擬,可預測訊號是否符合協定要求(如PCIe、USB、DDR),減少實驗室反覆修改。提前識別問題,降低修改成本與開發時程。

電源完整性關鍵指標

PDN阻抗與電壓穩定性

PDN阻抗過高會產生電壓漣波(Voltage Ripple)與IR Drop,影響高速介面(如SerDes、DDR5)穩定性。PI模擬可分析阻抗頻率響應,最佳化去耦電容配置與層疊設計,抑制電源雜訊。

預測供電瞬態與IR Drop

隨晶片切換頻率與電流需求增加,瞬態電流變化容易造成電壓下陷。PI模擬可預測不同負載條件下IR Drop與瞬態響應(Transient Response),提前修正PDN設計,避免供電不足導致時序錯誤或系統不穩定。

SIPI八大觀測指標

眼圖(Eye Diagram)

評估高速訊號穩定性與可碼性,確認其是否滿足如PCIe Gen5/6、USB4、DDR5 等協定所定義的Eye Mask規範(圖2)。眼圖的開口大小,是訊號是否可被正確讀取與通過合規驗證的首要門檻(圖3)。

抖動(Jitter)

抖動指的是訊號在時間軸上出現的晃動或偏移。可分為隨機性抖動(Random Jitter, RJ)與確定性抖動(Deterministic Jitter, DJ),影響時序裕度與資料正確性(圖4)。

時序偏移(Skew)

多條訊號因延遲不一致而導致的時間差,尤其在差分訊號與多位元並行傳輸中極為關鍵,會影響資料同步與眼圖對準。

阻抗匹配(Impedance)

阻抗控制是穩定訊號傳輸的基礎,確保走線、過孔或連接器阻抗連續,降低訊號反射(圖5)。

散射參數(S-Parameter)

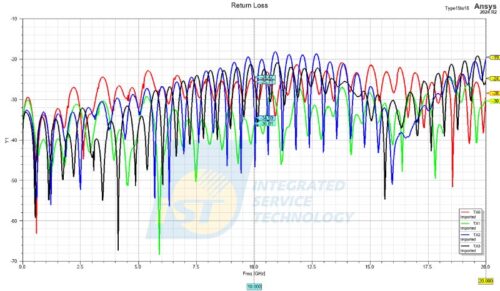

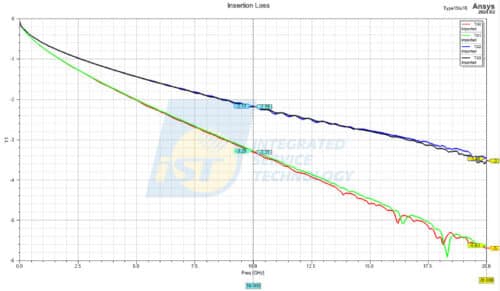

頻域分析的基本工具,常見指標為S11、S21,用於評估通道反射與插入損耗,驗證協定規範。

S11(Return Loss)代表訊號在發射端被反射回來的能量比率,是衡量阻抗不連續的關鍵指標(圖6)。S21(Insertion Loss)則表示訊號從輸入端傳到輸出端時因介質與導體造成的衰減(圖7)。

串音(Crosstalk)

當兩條或多條訊號線靠得太近,彼此的電場與磁場會互相耦合,造成近端(NEXT)與遠端(FEXT)串音(圖8)。模擬可優化走線間距、層間設計與屏蔽。

位元錯誤率(Bit Error Rate, BER)

BER代表每傳送多少位元中可能出錯幾次,是量化系統整體穩定性的重要指標。模擬能判斷是否需加入誤碼校正(Forward Error Correction, FEC)或均衡補償策略(Equalization, EQ),確保可解碼性。

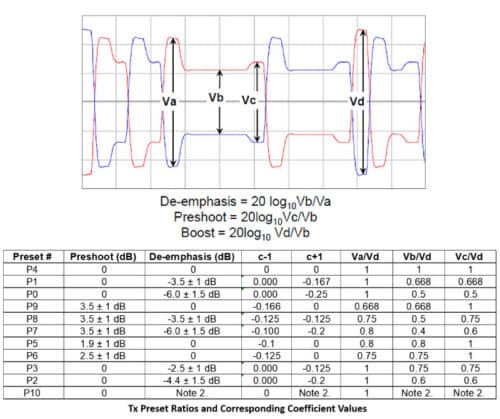

均衡補償(Equalization, EQ)

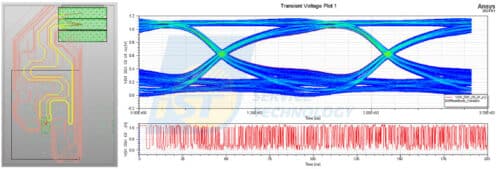

為因應訊號經過長距離與高損耗通道所產生的衰減與波形畸變,系統會配置TX預加強(Pre-emphasis)、RX均衡(CTLE、DFE),恢復長距離或高損耗通道波形(圖9、10)。

SIPI實施流程建議

- 建立模型庫

蒐集元件模型(IBIS、SPICE)、互連(S-parameter)、PDN資料,建立完整模擬資料庫。

- 前期預模擬(Pre-sim)

分析關鍵路徑的傳輸損耗、阻抗不連續與拓撲設計,同時評估PDN阻抗與去耦電容配置。

- 後期模擬(Post-sim)

導入實際版圖進行完整模擬,驗證眼圖、抖動、時序裕度及PDN噪訊等關鍵指標。

- 設計最佳化

根據模擬結果調整層疊結構、布線、終端與去耦電容位置與數量,平衡效能與成本。

- 實體測試比對

與實驗室測試結果比對,持續調整模型精度,確保SIPI模擬準確性。

在半導體與電子設計競賽中,高速傳輸已從加分項轉為基本門檻。導入SIPI模擬,可在設計階段預先掌握潛在風險,減少反覆試錯與設計迴圈,降低開發時程延誤與實驗室測試次數,節省人力與設備成本,確保高速產品穩定可靠上市。

(本文作者任職於宜特科技)