NVIDIA發布CUDA 13.1,推出革命性CUDA Tile技術,正式告別統治二十年的SIMT微觀管理模式。這項技術讓開發者從執行緒層級躍升至資料區塊層級操作,直接挑戰Google TPU在矩陣運算的原生優勢。

2006年,NVIDIA發明了CUDA,將GPU從單純的繪圖晶片解放為通用運算的神兵利器,這個「單指令多執行緒」(SIMT)模型統治了平行運算近二十年。然而,2025年12月4日,這家綠色巨頭卻親手拆掉了自己築起的圍牆。隨著CUDA 13.1發布,NVIDIA推出了「CUDA Tile」技術。

這不僅僅是一次版本更新,更是一場對抗硬體複雜度的豪賭。這代表著NVIDIA終於承認:在AI時代,強迫系統去管理每一條執行緒的死活,已經行不通了。

SIMT模式撞牆 人肉編譯難為繼

過去二十年,CUDA開發者的日常就像是用鑷子搬運沙子。為了榨出GPU的極致效能,工程師必須精細控制成千上萬條執行緒(Threads)的行為。這種SIMT模式在處理傳統圖學或簡單運算時游刃有餘,但在當今的AI時代卻撞上了鐵板。隨著硬體演進,GPU內部塞進了越來越多專用單元,例如專門處理矩陣運算的張量核心(Tensor Cores)和張量記憶體加速器(TMA)。

這些硬體怪獸雖然算力驚人,但要駕馭它們,開發者必須撰寫極度複雜的底層指令(如WMMA API)。這就像給了你一台F1賽車,卻要你用腳踏車的零件手冊來組裝它。開發者陷入了兩難:要麼花費數月手刻組合語言級別的最佳化代碼,要麼忍受低效能的上層框架。這種「人肉編譯器」的工作模式,正是AI演算法演進速度的最大瓶頸。

Tile技術核心 虛擬指令集當翻譯

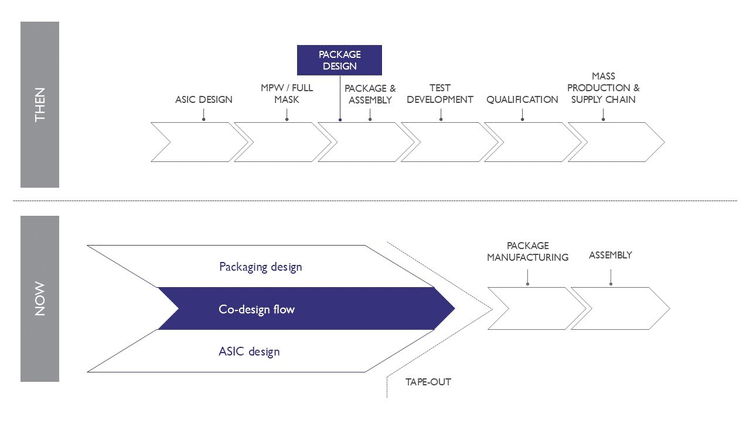

CUDA Tile的出現,徹底改變了這個遊戲規則。它不再要求開發者盯著每一個「點」(執行緒),而是允許開發者直接操作「面」(資料區塊,即Tile)。這項技術的核心在於引入了「CUDA Tile IR」(中介層)。這是一套虛擬指令集,充當了軟體與硬體之間的通用翻譯官。以前,當GPU架構從Hopper演進到Blackwell,底層的張量核心指令可能完全不同,開發者被迫重寫代碼。現在,開發者只需在Tile IR層定義「將A方塊與B方塊相乘」,剩下的髒活——如何將這些方塊映射到具體的執行緒、暫存器或張量核心上——全權交由編譯器與Runtime處理。

更具戰略意義的是cuTile Python的推出。NVIDIA這次直接繞過了C++的高牆,讓Python開發者也能透過類似NumPy的語法,直接呼叫底層的Tile指令。這相當於把核按鈕的發射器,裝在了一般大眾都買得起的遙控器上。這不僅降低了開發門檻,更是試圖將那些原本依賴OpenAI Triton或其他中介語言的開發者,重新拉回CUDA的原生懷抱。

TPU原生純粹 GPU軟體彌補差距

要真正看懂CUDA Tile的戰略價值,我們必須將目光轉向NVIDIA最大的隱形對手——Google TPU。Google的TPU(張量處理單元)打從娘胎裡出來,就是為了處理「方塊」的。TPU的核心架構是「脈動陣列」(Systolic Array),資料在晶片內部像波浪一樣規律流動,天生就是以矩陣(Tile)為單位進行運算。

因此,TPU的編譯器(XLA)在處理AI模型時擁有天然優勢,它不需要像GPU那樣,費盡心思去把矩陣拆解成執行緒,再把執行緒塞進核心裡。CUDA Tile的推出,實際上是NVIDIA在GPU架構上「模擬」了一種虛擬的TPU開發體驗。NVIDIA很清楚,雖然GPU的通用性無敵,但在AI專用運算上,SIMT模型的包袱太重。透過Tile IR,NVIDIA試圖達成一個不可能的任務:保留GPU處理各種雜亂運算的彈性(這是TPU的弱點),同時賦予開發者像操作TPU一樣直觀的矩陣運算能力。

這是一場「原生」與「演化」的對決。TPU贏在硬體純粹,效率極致但靈活性低;CUDA Tile則贏在生態包容,用軟體抽象層來彌補硬體架構的複雜度。

兩極社群反應 開發效率成最大權重

這項技術發布後,開發者社群的反應呈現有趣的兩極化。大部分被矩陣運算折磨的演算法工程師歡呼雀躍,認為終於可以從底層實作的泥淖中脫身,專注於演算法本身的創新。他們將cuTile視為「GPU程式設計的民主化時刻」。

然而,硬派的效能基本教義派卻持保留態度。在技術論壇上,像”DS.Zero”這樣的資深開發者直言不諱:「真正的進步應該是回到純C++,讓懂硬體的人榨乾每一個電晶體的效能。」他們的擔憂並非毫無道理。

任何抽象層(Abstraction Layer)都不可避免地會帶來效能損耗(Overhead)。當你把控制權交給編譯器,就意味著你放棄了挑戰物理極限的機會。但市場的風向已經很明顯。在AI模型參數邁向兆級的今天,開發效率(Time-to-Market)的權重早已超越了單點效能的極致最佳化。NVIDIA顯然算過這筆帳:損失5%的理論極限效能,換取開發速度提升500%,這才是商業世界買單的邏輯。

CUDA 13.1與Tile技術的問世,說明了NVIDIA正在進行一場自我革命。

黃仁勳很清楚,護城河不能只靠硬體堆料,更要靠軟體生態的易用性。透過將複雜的硬體細節封裝在Tile IR的黑盒子裡,NVIDIA正在對全球的開發者說:「你們只管去想像偉大的演算法,剩下的矽晶片難題,交給我。」或許會讓少數硬體極客(geek)感到失落,但對於整個AI產業來說,這無疑是按下了一顆加速鍵。

NVIDIA這次的作法也證明了,他們不只在Scale out方面積極仿效Google,連核心運算流程設計也不吝於學習Google,而且不是照抄,是深刻的利用了GPU的可程式化特性,最小化硬體變動,最大化軟體生態優勢。