imec在2025年國際電機電子工程師學會(IEEE)所舉辦的國際電子會議(IEDM)上,展示了包含單層二硒化鎢(WSe2)通道的p型場效電晶體(pFET)所具備的顯著性能升級,以及用於源極/汲極接點成形和閘極堆疊整合且與晶圓廠相容的改良版模組。這些研究成果透過imec與半導體製造商的合作來實現,為基於2D材料的元件技術之重大進展。

採用由2D過渡金屬二硫族化物(MX2)組成的原子級薄元件層來取代矽傳導通道,可望實現閘極與通道長度的極限微縮,同時保持良好的靜電通道控制與高載子遷移率。未來要實現的關鍵里程碑包含高品質的2D材料層沉積、閘極堆疊整合、低電阻源極/汲極接點成形,以及12吋晶圓整合。

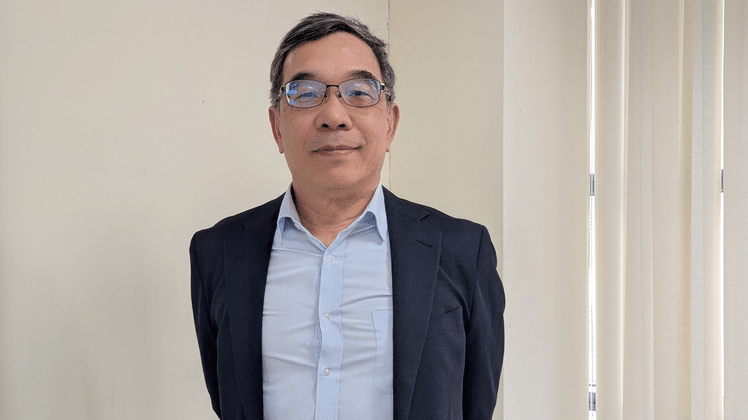

imec運算暨記憶體元件技術研發副總Gouri Sankar Kar表示,在2025年IEEE IEDM上,我們在兩場不同的發表會中展示,在imec核心CMOS產業聯盟計畫(IIAP)與半導體製造商建立的深度合作,如何實現2D材料型元件的性能突破。

Gouri Sankar Kar解釋,在過渡金屬二硫族化物通道的上方沉積頂層閘極二氧化鉿(HfO2)介電層,需要附加一層種子層來協助二氧化鉿形成晶核與材料成長。對nFET來說,這點透過形成一層氧化鋁(ALOx)介面層就能處理,但這套方法對pFET來說極具挑戰。與台積電合作,我們先是製作一層雙原子層合成二硒化鎢,該元件層的形成是將兩層由台積電提供的高品質二硒化鎢單原子層接續轉移到我們的基板上(圖1)。接著,我們把頂層二硒化鎢單原子層進行氧化,將其轉換為一層已經成功協助二氧化鉿閘極氧化層進行沉積的介面層。

另一場發表會則彰顯imec與英特爾合作開發用於n型(二硫化鎢與二硫化鉬)及p型(二硒化鎢)2D場效電晶體源極/汲極接點及閘極堆疊整合的12吋可製造模組。這項重大創新包含在英特爾的高品質2D材料層採用氧化物選擇性蝕刻製程,這些2D材料層由一層氧化鋁(ALOx)介面層、一層二氧化鉿層與一層二氧化矽(SiO2)層覆蓋(圖2)。氧化物蝕刻製程讓與晶圓廠相容的鑲嵌型頂層接點得以成形,為世界首例。

此項研究獲得imec產業聯盟計畫(IIAP)探索邏輯研究計畫(Exploratory Logic program)的資助,2D-PL試驗製程計畫則透過歐洲展望計畫(即Horizon Europe)與展望2020的補助協議。