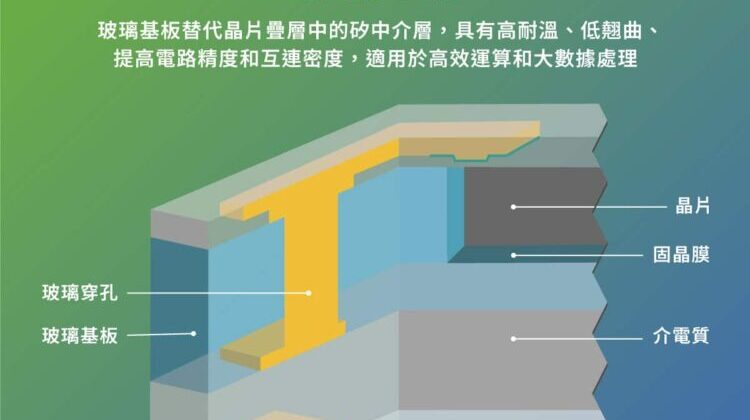

封裝設備業者Kulicke & Soffa(K&S)在SEMICON Taiwan 2023期間,揭露其免助焊劑熱壓接合技術,在OSAT產業引發關注。在2024年SEMICON Taiwan,K&S宣布該技術已經在客戶端成功導入。同時,K&S也推出可以在某種程度上替代矽穿孔(TSV)的垂直打線技術,實現更低成本的晶片堆疊封裝。

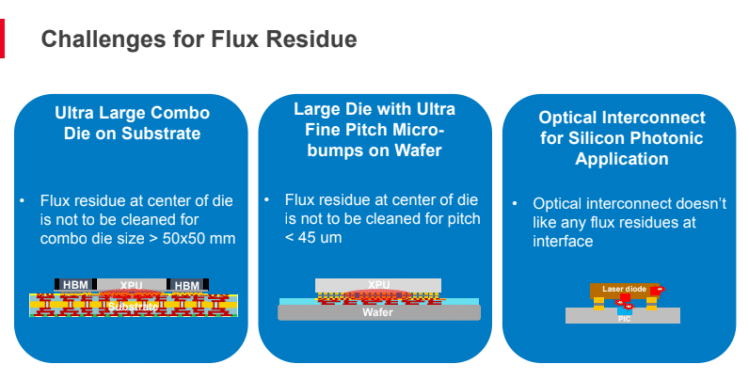

K&S先進封裝產品行銷資深經理鄭守鈞指出,助焊劑是焊接製程中常見的輔助材料,可以清潔焊接面並增加焊錫流動性。但在焊接完成後,助焊劑必須被清理乾淨,不能殘留在焊點上,所以在焊點隨著I/O密度提高而越來越小,晶片/基板的尺寸又不斷增加之際,如何徹底清除焊接後殘留的助焊劑,變成一大技術挑戰。如果能找到替代助焊劑的材料,封裝產業就可以用已經非常成熟的熱壓接合(Thermal Compress Bonding)技術,實現更高密度的I/O互聯。這是K&S與UCLA決定攜手合作,共同研究以原位甲酸(FA)取代傳統助焊劑的主要原因。

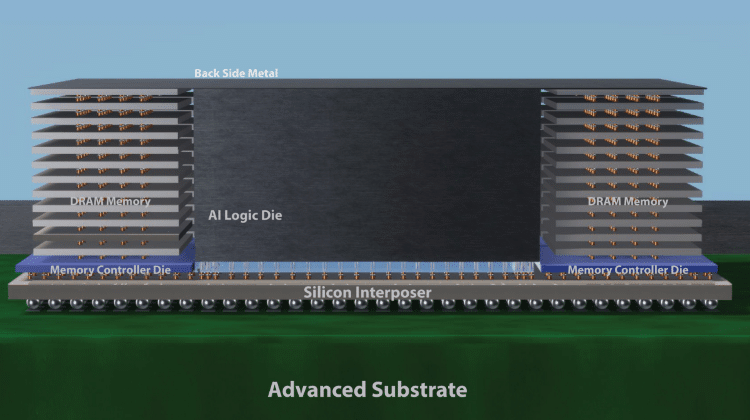

經過多年研究,目前這項技術已經實現商品化,例如K&S的APTURA無助焊劑TCB平台,就已成功將異質整合及小晶片的微型凸塊從35µm焊接間距縮小到10µm,讓超微間距micro-bump互連得以實現,進一步導入量產。除此之外,這台設備還能實現無凸點銅對銅直接焊接。目前已有部分台灣用戶將其應用在手機、HBM、矽光子、AI、HPC、伺服器元件的生產中。

除了分享無助焊劑TCB技術的最新進展外,K&S在SEMICON Taiwan 2024期間,也介紹了新型的垂直打線(Verticle Bonding)技術。由於2.5D、3D封裝興起,不管是晶片對晶片或晶片對基板,需要垂直互聯的情況明顯增加,因此TSV製程開始流行起來。但TSV的加工成本相對高昂,而且在晶片設計時,必須在晶片上預留給TSV通過的空間,因此當TSV數量增加時,晶片面積的使用效率難免會受到影響。如果打線技術能打出垂直方向的導線,在某些應用中,打線技術就有潛力成為一種比TSV更具成本效益的連線方式。

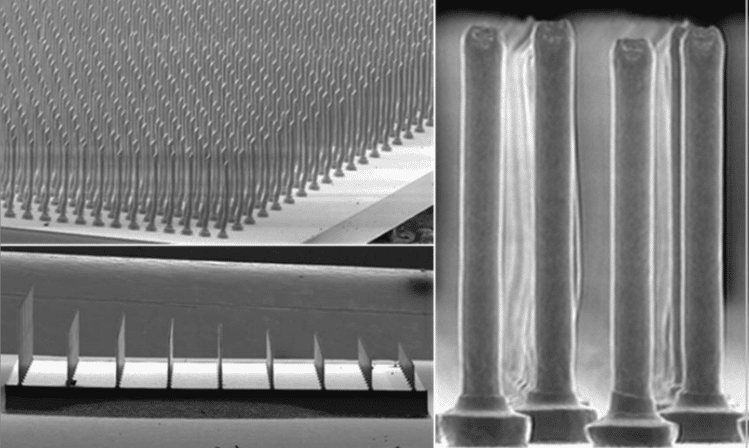

K&S球焊產品行銷資深經理黃山壽介紹,從前面提到的基本概念出發,K&S已發展出可以直接在晶圓上拉出垂直導線的垂直打線技術,並且被實際應用在記憶體堆疊封裝跟電磁屏蔽(EMI Shielding)上。目前K&S的垂直打線技術最小間距可以做到40µm,打線的垂直高度最高可以到1.3公厘。配合垂直打線展示的ATPremier MEM PLUS,是目前業界速度最快的的晶圓級焊接機,配備K&S獨有的結果導向工藝能擴展製程寬度、提升作業效率和產品可靠性。

由於垂直打線所使用的金屬材料大多是材質偏軟的金線,因此垂直打線所拉出來的導線會有一些彎曲現象產生。目前K&S還在繼續努力,希望能拉出更筆直的垂直導線,以滿足更嚴格的應用要求。

K&S執行副總裁兼總經理張贊彬總結說,作為全球封裝設備的主要供應商,K&S一直在思考如何讓OSAT業者能盡可能沿用已經很熟悉的製程技術跟廠房基礎設施,滿足客戶對先進封裝的需求。不管是混和接合或TSV,這些先進封裝技術雖然都能實現更小的Pitch,但OSAT卻得為此導入晶圓廠等級設備跟廠務設施,造成巨大的資本支出。無助焊劑TCB跟垂直打線技術都可以讓OSAT廠在既有的生產環境中,製造出Pitch比傳統封裝更小的互聯,進而讓OSAT廠在資本支出可控的前提下,滿足客戶的需求。