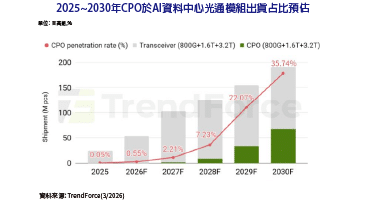

NVIDIA的Blackwell世代將銅線傳輸逼至物理極限,迫使2027年Rubin Ultra全面導入共同封裝光學技術。這場把光電轉換引擎直接封裝於晶片旁的「體內手術」,能耗可降七成,而台灣矽光子供應鏈正是這場豪賭的核心執刀團隊。

NVIDIA的Blackwell世代雖然取得了空前成功,但也把「銅線傳輸」這項技術壓榨到了最後一滴油。當黃仁勳準備揭開2027年Rubin Ultra的面紗時,工程師們面臨一個極其殘酷的現實:電訊號跑不動了。這不是誇飾。當單一GPGPU的傳輸頻寬暴漲至28.8Tb/s,傳統電子訊號在電路板上的有效傳輸距離縮短得像一張信用卡那麼寬。為了不讓訊號死在半路上,NVIDIA被迫啟動一場極其大膽的「體內手術」——共同封裝光學(CPO)。這不再是單純的技術升級,這是一場關於生存的豪賭。

損耗帳算不過 光電共封砍七成

要理解這場革命,你得先看懂「損耗」這筆帳。在過去的架構裡,數據從GPU出發,要經過載板、PCB、連接器,最後才到達機殼邊緣的光模組(Pluggable Transceiver)轉成光。這段路程雖短,但在224G SerDes的超高速率下,電訊號就像在泥沼裡跑步,能耗驚人。

根據最新的技術白皮書,如果Rubin Ultra堅持沿用傳統設計,光是「搬運數據」所消耗的電力,就會吃掉整座資料中心40%的能源預算。這意味著你買了一台法拉利,卻把一半的油耗在怠速上。CPO的邏輯很簡單也很暴力:把轉運站直接蓋在工廠裡。它將光電轉換引擎(Optical Engine, OE)直接封裝在晶片旁邊,把電訊號的傳輸距離從「英吋」縮短到「毫米」。這唯一的一步,直接讓能耗暴跌70%,為Rubin Ultra的全液冷架構留下了活路。

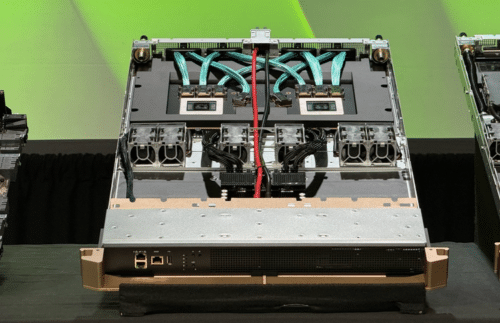

雙櫃百顆互連 光引擎變晶片器官

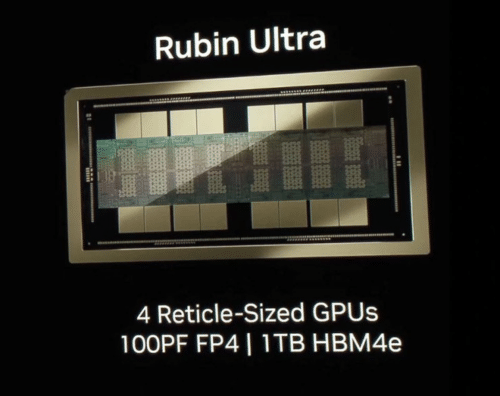

Rubin Ultra的設計圖,簡直就是工程師對物理極限的挑釁。NVIDIA這次不滿足於單櫃,而是推出了NVL72x2的雙櫃互連架構,將144顆GPU(總計576個GPU Dies)融合成一個超級大腦。要在這麼短的距離內,讓144顆大腦同步思考,Scale-Up網路(機櫃內互連)成了絕對關鍵。這裡,我們看到了一個驚人的數據配置:NVSwitch的進化方面,每一顆NVSwitch交換晶片,都與4.5顆3.2T的光學引擎封裝在一起(為什麼是0.5?因為有一顆引擎的頻寬被相鄰晶片共享),這讓單顆Switch的吞吐量達到14.4T。

密度方面,一座Rubin Ultra雙機櫃,需要144顆這樣的CPO NVSwitch,光是為了讓這些GPU互相說話,就得在機櫃裡塞進648顆光學引擎。若算上負責對外溝通(Scale-Out)的CX10網卡也全面CPO化,整座機櫃的光學引擎總數將達到792顆。平均下來,每1顆GPU需要5.5顆光學引擎來伺候。這個數字標誌著一個時代的結束:光學元件不再是外掛的配件,它已經變成了晶片的「器官」。

兩杯毒藥的抉擇 良率決定誰能量產

然而,故事並不是「NVIDIA決定用CPO,然後世界就和平了」這麼簡單。事實上,直到2026年的今天,供應鏈內部仍瀰漫著一股焦慮感。因為擺在黃仁勳面前的,是兩杯都不好喝的毒藥。第一條路是正交背板(Orthogonal Backplane),這是傳統派的最後掙扎。

為了不改動封裝,工程師試圖讓計算托盤(Compute Tray)與交換托盤(Switch Tray)直接呈90度垂直對插,省去線纜。代價是需要製造厚度超過80層、且必須使用極低損耗材料(如石英纖維)的超級PCB,鑽孔良率低得嚇人,且組裝難度極高,稍有不慎就會折斷針腳。第二條路是CPO(共同封裝光學),這是未來派的賭注,效能完美,但它有一個致命傷——「不可重工(Non-reworkable)」。

想像一下,一個NVSwitch托盤上封裝了6顆Switch和27顆光引擎,只要其中一顆光引擎在出廠測試時壞了,或是光纖對準歪了1微米,整片造價數十萬美元的板子就得直接報廢,你不能像修手機一樣只換零件。這就是為什麼NVIDIA至今仍維持「雙軌並行」的原因。2027年誰能勝出,不看誰的PPT做得漂亮,而是看誰能把良率從「賭博」變成「量產」。

台灣供應鏈執刀 縫合光與電兩個世界

在這場良率的生死戰中,NVIDIA必須依賴一群能把良率做到極致的「執刀醫生」。而這群醫生,剛好都聚集在台灣。Rubin Ultra的CPO方案若要落地,以下四個環節缺一不可。

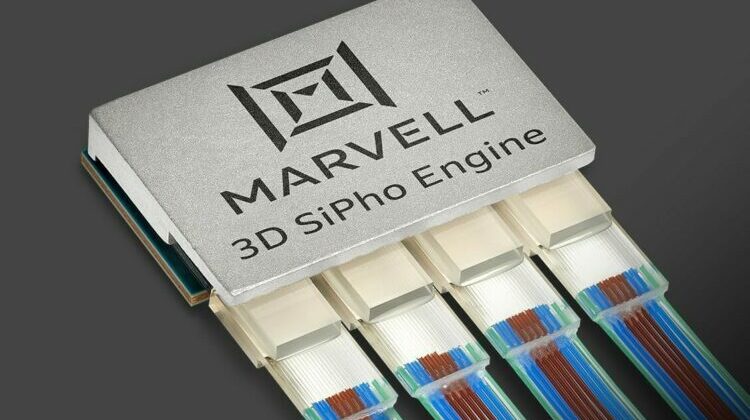

台積電COUPE:矽光子的地基

一切的起點是台積電的COUPE(緊湊型通用光子引擎)。這不是普通的封裝,而是利用SoIC-X技術,將電子的EIC晶片直接「堆疊」在光子的PIC晶片上。這種3D堆疊去除了傳統的凸塊(Bump),將寄生電容降到最低,是CPO能跑上3.2T速率的物理基礎。沒有台積電,CPO就只是紙上談兵。

封裝雙雄:日月光與訊芯的戰場

當晶片離開台積電,真正的惡夢——「異質整合」才剛開始。訊芯-KY(6451)挾著博通(Broadcom)與CPO龍頭的合作經驗,掌握了光電模組的量產密碼,在Rubin世代,他們負責將那些脆弱的光學引擎穩穩地固定在基板上。日月光(3711)則利用其VIPack平台中的FO-EB(扇出型嵌入式橋接)技術,解決了CPO帶來的極端散熱與訊號佈線挑戰。

光路對準:上詮與奇景的微米戰爭

這是良率最容易崩盤的環節。要在封裝體內將光纖與矽光晶片精準對接(Coupling),誤差容許值只有微米等級。上詮(3363)與奇景光電(Himax)聯手開發的解決方案,利用WLO(晶圓級光學)技術製造微透鏡陣列,並配合特殊的FAU(光纖陣列單元),就像是幫光訊號裝上了「導航系統」,確保光能無損地射入光纖。這項技術是提升CPO良率的關鍵鑰匙。

散熱的最後一哩:聯鈞與外部光源

CPO最怕熱,因為雷射二極體對溫度極度敏感。因此,NVIDIA採取了ELS(外部雷射光源)策略,把發熱的雷射移到機櫃門口。聯鈞(3450)在這裡扮演了關鍵角色,作為高階雷射封裝的老將,他們提供的矽光子雷射模組,讓光源可以像電池一樣「隨插即拔」。這不僅解決了散熱問題,也規避了「雷射壞掉導致整機報廢」的風險。

Rubin Ultra的CPO革命,本質上是一次權力的重新分配。過去,網通廠、光模組廠、晶片廠各據一方;但在2027年之後,界線將被抹去。NVIDIA透過CPO,將光學通訊收編為晶片設計的一部分。

對於供應鏈來說,這是一張單程車票:要嘛進化成高精度的矽光子整合商,要嘛看著訂單歸零。而在這場轉型風暴的中心,台灣供應鏈不再只是代工者,而是唯一能幫NVIDIA縫合「光」與「電」這兩個世界的縫合師。