台灣憑藉在CoWoS、3D IC等關鍵技術的領先優勢,正從傳統代工基地蛻變為全球半導體創新中心。在這場後摩爾時代的競爭中,台灣如何把握機遇、重塑產業地位?

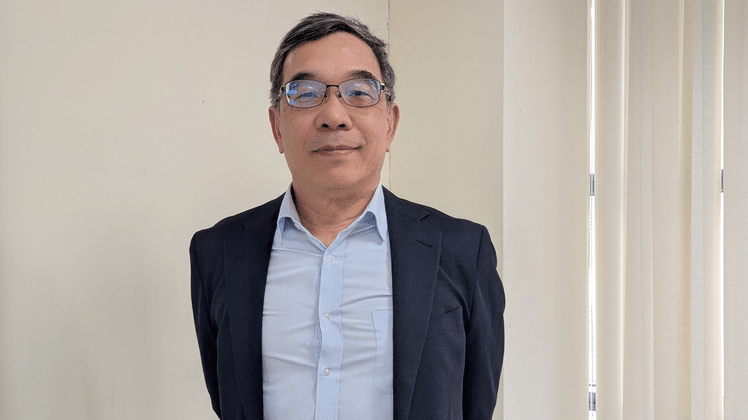

工研院電光系統研究所副所長駱韋仲接受專訪時指出,AI浪潮為台灣半導體產業帶來前所未有的戰略機遇,先進封裝技術正是推動這波成長的核心引擎。從CoWoS到3D IC,從矽光封裝到系統整合,台灣正在這些關鍵技術領域建立新的競爭優勢,重新定義在全球半導體產業鏈中的戰略地位。

摩爾定律遭遇極限 先進封裝開啟雙軌發展新紀元

目前摩爾定律的延續呈現雙軌並行的發展模式。第一條路徑是傳統的製程微縮化,在可預見的十年內仍會持續推進,從目前的兩奈米繼續向更先進的節點邁進,只是需要付出更高的成本代價。第二條路徑則是系統級整合,也就是透過先進封裝技術實現的晶圓級系統整合。

駱韋仲表示,這種系統整合的優勢在於可以透過晶片堆疊實現電晶體數量的倍增。例如兩顆晶片堆疊就能達到兩倍的電晶體密度,三顆堆疊則是三倍。更重要的是,這種架構可以將不同功能的元件整合在一起,包括邏輯運算、記憶體,甚至AI專用晶片,實現異質整合的效果。

他特別強調,在AI應用中,系統不會只有單一晶片,而是需要整合記憶體、CPU、GPU等多種元件。這種複雜的整合需求,正是先進封裝技術發揮關鍵作用的領域。

這種技術典範的轉移,不僅為台灣半導體產業提供了新的成長動能,更為全球科技發展開闢了新的可能性。當單純的製程微縮面臨瓶頸時,先進封裝技術提供了延續摩爾定律精神的全新路徑。

AI需求引爆產能荒 CoWoS供應鏈迎來黃金成長期

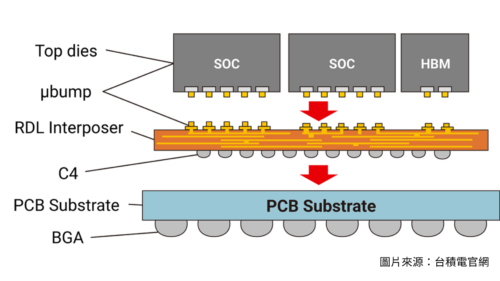

駱韋仲認為,AI浪潮在半導體領域必然是最重要的發展情境。他分析指出,AI網路架構的複雜性決定了先進封裝技術的必要性。AI網路不會只依賴單顆IC,而是需要整合記憶體,同時在邏輯晶片中既要有CPU也要有GPU。這種多元異質整合的需求,非得用先進封裝來整合才能實現。

談到台灣在這波AI浪潮中的優勢,駱韋仲指出,台灣的CoWoS技術已是業界公認的領先技術。所有人都知道CoWoS是2.5D技術,這種技術專門承載高速運算的邏輯晶片、AI晶片加上記憶體等元件的整合,這個技術優勢已經確立。

駱韋仲強調,製程微縮化還在持續進行,在可預見的十年內還會持續微縮。雖然兩奈米之後的技術節點微縮要付出較高代價,但問題不在於技術可行性,而是成本考量。在這種背景下,系統整合架構就變得更加重要,而且是發生在晶圓級的系統整合。

他進一步解釋,現在台積電的技術路線圖主要還是圍繞電晶體數目的提升,也就是摩爾定律的核心概念。但在AI浪潮裡,系統端的考量變得非常關鍵,因為它可以實現電晶體數目的倍增,同時在不同應用部分具備系統性的優勢。

3D IC與矽光技術領跑 台灣搶占後摩爾時代制高點

駱韋仲看好真正的3D IC技術前景,他以人眼為例解釋這種技術的運作原理。據他說明,真正的3D IC就像是人眼一樣,有一個感測器,感測器之後會迅速把這些感測的類比訊號傳到記憶體IC,並送到ISP等相關運算架構處理。這種垂直整合的架構可以大幅提升處理效率並降低功耗。

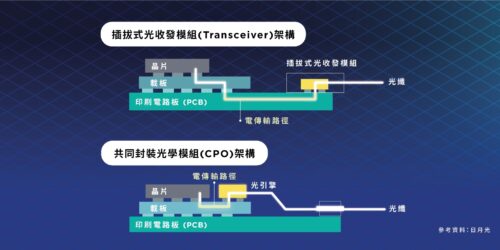

除了3D IC,駱韋仲特別看好矽光封裝技術的發展前景。他認為矽光封裝最大的優勢在於能耗可以降得非常低,第二個優勢是傳輸的資料量越來越高。矽光子技術預期能將傳輸速度提升至3.2 T以上,這種技術突破的意義在數據中心應用場景中格外重要。

然而,矽光技術的產業化仍面臨挑戰。駱韋仲坦言,台灣在這個領域的產業鏈尚不完整,工研院結合產業界、學界透過SEMI SiPhIA聯盟及TOSIA聯盟正積極推動產業鏈的建構。他表示,工研院主要扮演三個重要功能。首先是產業鏈結的推動者,特別是在產業鏈還不完整的領域,如矽光子技術,工研院會結合業界共同推動產業鏈的建立。

其次是技術平台的提供者。駱韋仲說明,工研院推動research foundry的概念,提供先進封裝的研究平台,讓全世界的研發單位可以在台灣進行前瞻技術的驗證。這種模式初步以協助國內為主,有了初步成效後再推動到全球合作。

第三是跨領域整合的優勢。工研院不會針對單一技術,而是透過不同的研究單位,從材料、設備各方面進行共同優化。這種跨領域的結合能力,讓工研院在整合性技術開發上具有獨特優勢。

駱韋仲特別提到,如果research foundry概念能夠成功,未來技術留在台灣生產的機會就非常高。這種前瞻研究與量產技術的連結,正是台灣維持半導體領先地位的關鍵策略。

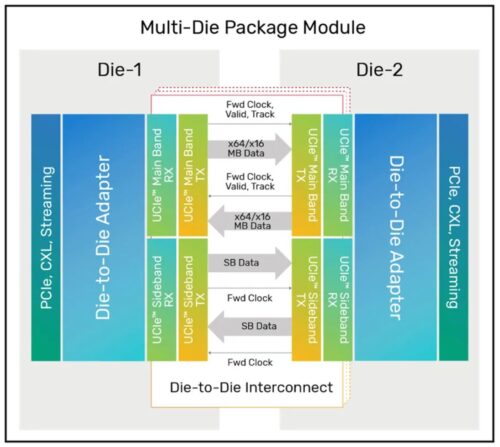

談到小晶片技術,駱韋仲指出小晶片設計最初是為了解決大晶片良率低、成本高的問題,透過將大晶片切分為較小的單元來提高生產效率。現在的小晶片設計已經發展到考慮架構優勢,不僅是提高良率,更要實現功能的模組化整合。

談到產業標準化,駱韋仲表示,國內在UCIe(Universal Chiplet Interconnect Express)標準的參與度很高,工研院也經常與UCIe主席進行技術交流。UCIe作為小晶片互連的開放標準,正在推動整個產業生態系統的建立,讓不同廠商的小晶片能夠實現互相相容的整合。

他認為,理想的小晶片生態系統應該像百貨公司一樣,客戶可以根據需求選購不同功能的晶片進行組合。雖然目前還無法完全實現這種標準化,但透過EDA工具的配合以及設計端的主導,這個目標正在逐步實現。

從代工基地到創新中心 台灣半導體戰略地位重新定義

駱韋仲分析台灣在先進封裝領域的競爭優勢時指出,台灣必須善用現有的製造優勢,結合先進封裝技術的發展。他認為,台灣要做好先進封裝,第一個必須要先把IC做好,在製造端必然在全球能見度非常高,而且是領先的。

在產業分工方面,駱韋仲提到,類似SK Hynix的案例說明了開放合作的重要性。SK Hynix原本在記憶體HBM方面相對落後,但透過先進封裝的整合,願意比較開放地把一些與記憶體相關的介面控制方式與台積電技術做連結和驗證,最終在AI浪潮興起時大幅領先。

他強調,台灣一定要與現有的優勢做整合結合,讓台灣擁有這個優勢。第二個部分是設備材料的在地化,他認為至少先進封裝50%要能夠做到在地化、國產化,這樣才能更快速、更有效率地進行技術創新和迭代。

發展路徑方面,他認為台灣必須先把2.5D先進封裝做好,再逐步拓展到更先進技術領域。台灣憑藉CoWoS技術領先地位,角色正從代工基地轉向創新中心。除技術研發外,應用端對接同樣重要,先進封裝與系統整合在不同應用場景將創造差異化優勢。

展望未來,駱韋仲認為半導體產業將朝向更多元化的發展。除了持續的製程微縮,系統整合和先進封裝將扮演越來越重要的角色。他特別看好矽光技術、化合物半導體,以及新興的三維積體電路技術。

在應用領域方面,駱韋仲提到智慧製造和工業用機器人將是重要的發展方向。相較於消費性產品,工業應用對於先進封裝技術有更高的必要性和成本承受能力。台灣在這些領域的系統公司優勢,結合先進封裝技術,將創造新的競爭優勢。

駱韋仲總結,面對國際競爭和地緣政治的挑戰,台灣必須加速技術創新和產業升級。透過先進封裝技術的發展,結合既有的製造優勢,台灣有機會在後摩爾時代繼續維持半導體產業的領先地位。他強調,這需要政府、學術界和產業界的通力合作,持續投入研發資源,才能在激烈的國際競爭中脫穎而出。