電子設計自動化(EDA)工具業者益華電腦(Cadence)近日宣布推出「從規格到封裝成品」(Spec-to-Packaged Parts)的Chiplet生態系,以降低工程複雜性,專為開發物理AI、資料中心、高效能運算(HPC)應用之Chiplet客戶加速上市時間。首批加入Cadence生態系的IP合作夥伴包括Arm、Arteris、力旺電子、円星科技、Silicon Creations與Trilinear Technologies,以及矽分析合作夥伴proteanTecs。為降低風險並簡化客戶導入流程,Cadence正與三星晶圓代工合作,打造Cadence物理AI小晶片平台的矽原型,並於三星晶圓代工SF5A 製程中預先整合合作夥伴的IP。

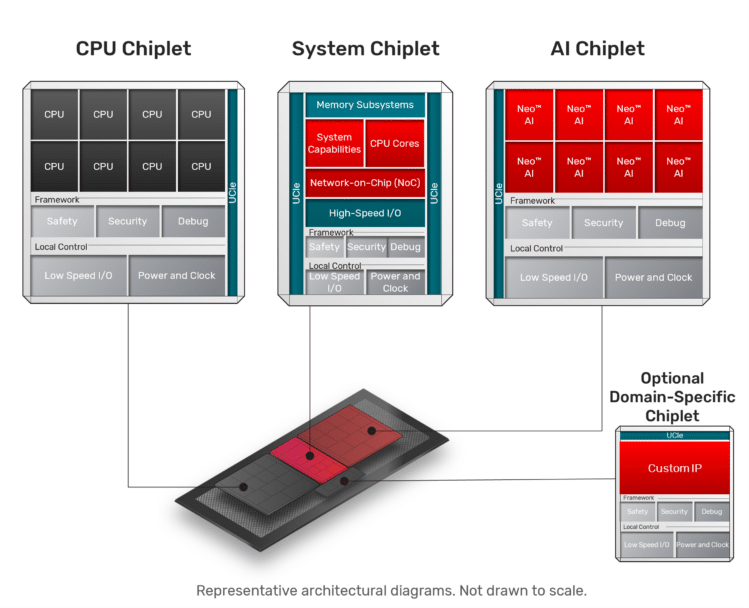

延續長期的深度合作,Cadence 與Arm亦攜手加速物理AI與基礎架構AI應用的創新。Cadence將利用先進的Arm Zena運算次子系統(CSS)與關鍵 IP,強化其物理AI小晶片平台與框架。這項全新的解決方案能滿足汽車、機器人與無人機對次世代邊緣AI處理的嚴苛要求,並符合資料中心、雲端及HPC應用對標準化I/O與記憶體小晶片的需求。此聯盟不僅降低了工程複雜性,更為客戶提供採用先進小晶片的低風險路徑,為更聰明、安全且高效的系統奠定基礎。

Cadence運算解決方案事業群副總裁David Glasco表示,隨設計複雜度提升,多晶片架構對於實現卓越效能與成本效益十分關鍵。Cadence的Chiplet解決方案能優化成本並提供高度客製化彈性。透過整合我們豐富的SoC設計專業與生態系中預先驗證的IP,我們正協助客戶降低風險,更有信心快速實現Chiplet開發目標。

Cadence已建構規格驅動的自動化系統,可生成結合Cadence IP與各方IP的Chiplet框架,並具備管理、安全性與安全防護功能。在EDA工具流程上,該架構支援Cadence Xcelium邏輯模擬器進行無縫模擬,並透過 Palladium Z3企業級模擬平台進行硬體模擬;在實體設計上,則利用即時回饋優化布局布線週期。此外,該架構完全符合Arm Chiplet System Architecture與未來的OCP規範,確保跨生態系的互操作性。透過 Cadence的UCIe IP,能提供業界標準的晶片對晶片連接,並支援LPDDR6/5X、PCIe 7.0及HBM4等介面。

Cadence物理AI Chiplet平台的部分基礎系統原型,已預先整合了Cadence Chiplet框架、UCIe 32G、LPDDR5X IP,並已成功通過全矽驗證。