益華電腦(Cadence)宣布,與經濟部產業技術司攜手合作的「全流程智慧系統設計實現自動化研發夥伴計畫」締造重大里程碑。此計畫成功協助工研院建構全台首創的「全流程3D IC智慧系統設計與驗證服務平台」,推出3D異質堆疊晶片設計服務(3D IC Turnkey Design Service)、異質整合封裝驗證流程與共乘服務(Heterogeneous Integration Shuttle Service)、記憶體-邏輯堆疊(Memory-on-Logic) AI晶片技術MOSAIC,並勇奪2024年全球百大科技研發獎。

根據Fortune Business Insights預估,生成式AI市場規模,將從2024年的670億美元,增長到2032年的9,676億美元,年均複合成長率高達39.6%。為協助產業加速導入生成式AI應用, Cadence與工研院攜手合作,設立「AI感知運算系統共創實驗室」,提供全流程(晶片-封裝-系統)設計與驗證服務,已直接服務中小型企業與新創12家,大型企業7家,協助台灣產業參與AI的商機,例如工研院已與金融科技業者合作,利用AI技術,推出新金融服務。

經濟部產業技術司司長郭肇中表示,本次經濟部與Cadence的合作,成功協助工研院建立台灣首創全流程3D-IC智慧設計驗證平台與AI感知運算系統共創實驗室,為國內半導體產業注入了強勁的創新能量,帶動AI產業應用落地。AI技術已成為驅動未來產業發展的核心動力,透過與Cadence這樣具備全球領先技術的夥伴合作,將能加速台灣在AI晶片設計領域的發展,提升整體產業的國際競爭力。

Cadence與經濟部、工研院的聯合展示聚焦三大主題,分別是3D IC Turnkey服務、AI智慧金融方案與Agentic AI賦能晶片設計自動化。同時還特別邀請到經濟部產業技術司司長郭肇中親臨現場,與Cadence資深副總裁暨數位與簽核事業群總經理滕晉慶,就雙方合作的豐碩成果與未來發展進行深入交流。此外,活動更匯聚產學研各界領袖,包括群聯電子執行長潘健成、工研院電光系統所所長張世杰、清華大學半導體學院副院長劉靖家教授、台灣大學電子工程學系所長江介宏教授,以及Cadence研發副總裁Don Chan等專家共同激盪GenIC技術的創新思維。

全流程3D-IC智慧系統設計與驗證服務平台

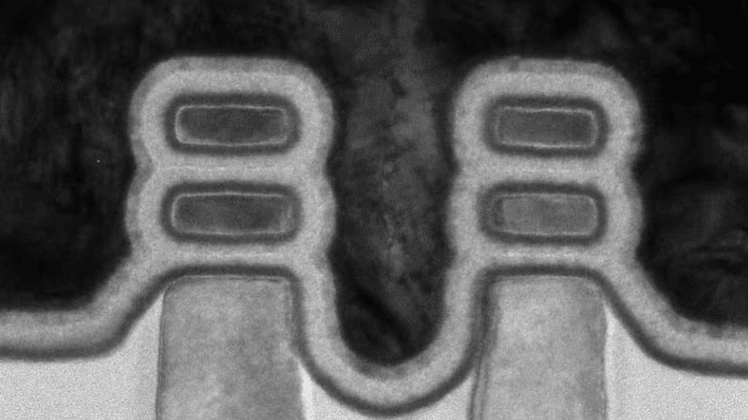

為滿足未來高效能運算需求,3D-IC堆疊與小晶片異質整合已成為延續摩爾定律的關鍵策略。針對3D-IC設計與異質整合所面臨的複雜挑戰,Cadence與工研院攜手合作的全流程3D-IC智慧系統設計與驗證服務平台,全面採用Cadence領先的3D-IC全流程技術,成功整合設計、分析與驗證等核心環節,將為台灣半導體產業注入強勁的創新動能。透過此平台,工研院已成功協助產業夥伴實現AI晶片的應用落地,充分展現其在加速產品開發和提升設計效率方面的卓越成效。

探索晶片設計自動化技術 – GenIC 生成式晶片設計自動化

隨著 AI 晶片與系統設計複雜度的大幅躍升,晶片設計流程正經歷深刻的轉型。從過去典型的腳本式晶片設計自動化,逐步進化導入 AI 智慧輔助(Copilot)的設計自動化流程,未來更將邁向代理人AI(Agentic AI)的發展趨勢。代理人AI以大型語言模型(LLM)為基礎,並採用自然語言(NL)作為設計介面,能協助設計研發人員探索更大規模、更多元的晶片架構,同時優化功耗、效能、面積與時程,進一步提升晶片設計開發與生產效率。多年來,Cadence以其AI驅動平台引領EDA產業,協助客戶在設計流程中導入生成式AI。憑藉深厚的AI研發實力,並藉由本次合作平台為媒介,Cadence 將攜手產官學研各界,共同探索新興的GenIC生成式晶片設計自動化技術,期能為台灣乃至全球AI產業注入創新能量。

Cadence台灣益華總經理宋栢安表示,我們非常榮幸能與經濟部及工研院攜手合作,共同打造這個具備里程碑意義的3D IC智慧設計驗證平台。這項成果不僅展現了Cadence在全流程智慧系統設計上的領先地位,更證明了透過產官學研的緊密合作,能夠有效推動技術創新與應用落地。有了此平台的成功經驗,Cadence將持續強化與台灣產官學研的合作夥伴關係,憑藉全流程設計的深厚實力,助力生成式晶片設計自動化的發展與應用,為台灣半導體產業注入創新動能、開創產業發展的新契機。