目前市場上多種晶片應用在日常可及的電子產品中,讓生活變得便捷、有趣。但是,當它們默默支撐起智慧生活時,人們也該知道,一款晶片從最初的發想到最後的量產出貨,背後其實經歷相當繁複的設計和製造流程。

電子設計自動化(Electronics Design Automation, EDA)工具就是晶片設計中至關重要的環節,正因為有了它,設計工程師可將晶片的電路設計、效效能分析、IC版圖、功能驗證等過程交由電腦自動處理完成,大幅提升設計和驗證效率,如果沒有EDA工具,僅依賴原始的手工製程,大型積體電路設計幾乎是一項不可能完成的任務。

EDA軟體在晶片方法學中被賦予新意義

時至今日,全球晶片產業進入軍備賽,高效能計算、人工智慧(AI)技術等深入到晶片設計領域,這對EDA工具再次提出顛覆性的挑戰,在發展週期中,EDA也被賦予新的意義。

日前,Cadence公司亞太區系統解決方案資深總監張永專表示,軟體已經成為能不能成功做出一顆好IC的關鍵,所有晶片設計的最終挑戰都來自於軟體。

對很多公司來說,IC設計往往需要多次流片進行驗證,耗時久、成本高,在這樣的情況下,由於晶片算力不斷提升、設計越來越複雜,軟體和驗證成本所占比例正不斷增加。

張永專認為,未來五年系統和晶片設計廠商將面臨上市時間(Time-to-market)的壓力,以及異構多核、高算力、差異化創新、系統與軟體堆疊所帶來的技術挑戰,由此帶來的軟硬體協同設計和超過80%的IP複用問題,導致驗證工作日趨複雜,開發人員不得不將60%以上的精力用於軟體。

張永專表示,軟體正在主導晶片開發的成本、流程和週期,Cadence以及其他EDA廠商都希望在晶片正式流片之前,盡早透過完整的系統級驗證與模擬,對晶片的效能、功耗、軟硬體進行測試,這也符合當前主流設計流程中所體現的提前測試(Shift Left)趨勢,也就是說,在RTL實現前就要完成相關的軟體發展驗證工作。

提升矽前硬體除錯及軟體驗證速度

基於這些趨勢,Cadence認為有幾個扭轉局勢的關鍵點,第一,模擬需要通過硬體的方式得以加速,反覆運算的速度非常重要;第二,原型驗證系統必須能容納大規模晶片,容量是關鍵;第三,需要快速調試、準確預測編譯結果。

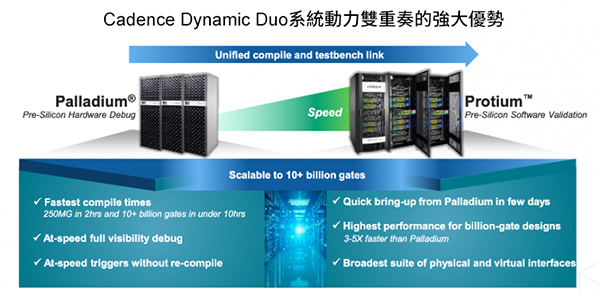

今年4月,Cadence推出Palladium Z2企業級硬體模擬加速系統和Protium X2企業級原型驗證系統,希望透過硬體模擬加速(Emulation)和原型驗證(Prototyping)工具,確保上述關鍵得以實現。Palladium Z2+ Protium X2這一組合被Cadence稱為動力雙重奏(Dynamic Duo)系統系統動力雙重奏,為系統模擬和驗證提供較佳的效能和容量支援。

Palladium Z2硬體模擬加速平台基於Cadence全新的自定制硬體模擬處理器,可提供較佳的編譯速度和矽前硬體除錯功能。Protium X2原型驗證系統,基於Xilinx UltraScale+ VU19P FPGA,為10億門級的晶片設計,提供矽前軟體驗證所需的運行速度和初始啟動時間。

張永專表示,動力雙重奏系統動力雙重奏整合編譯器和外設介面是關鍵。此外,模組化編譯技術也應用在兩個系統中,使得100億門SoC的編譯工作,透過Palladium Z2系統可在10小時內完成,Protium X2系統也僅需不到24小時就可以完成,使用者可提升2倍容量和1.5倍效能,在更短的時間為大規模晶片驗證完成更多次數的反覆運算。

為擴大應用範圍,Palladium Z2和Protium X2在四個層面進行優化,首先,支援包括RTL、Verilog、VHDL在內的所有硬體設計;其次,可以和虛擬模型同時進行模擬;第三,硬體加速器支援DDR4/DDR5/HBM/UFS等多元的記憶體類型;最後,為PCIE、USB、Ethernet等介面協定,提供相應的實際物理介面。

兩個硬體平台值得關注

Palladium Z2硬體模擬加速平台基於Cadence的自定制硬體模擬處理器,Protium X2原型驗證系統則基於FPGA。

張永專說明,模擬產品要在模擬精確度和速度提升之間,尋找「精妙的平衡」。在硬體模擬方面,業界其它產品都採用FPGA架構。但基於FPGA架構的產品對硬體模擬而言,在RTL Code完全穩定之前,除錯和模擬速度只能擇一,FPGA其實很難實現快速反覆運算,無法真正節省開發時間,與之相比,Palladium的硬體模擬核心處理器由Cadence定制開發,與上一代產品相比,除了處理器的製程更新之外,還採用特殊設計以實現硬體模擬加速,可提供更快的編譯速度和矽前硬體除錯功能。

至於Protium X2為什麼基於FPGA處理器?原因在於矽前軟體驗證屬於軟體調試範疇而非硬體除錯,透過通用型FPGA處理器,能夠享受先進製程和穩定效能所帶來的高運行速度、最短初始啟動時間以及降低成本。

這些設計上的突破也使Cadence實現差異化的特點。張永專認為,硬體模擬和軟體模擬在未來的應用中各有千秋。軟體模擬運行在伺服器上,整體成本比硬體加速還低,非常適合形式驗證、IP級模擬等應用;對於規模更加龐大的SoC晶片驗證、軟體調試、原型驗證等工作,則需Palladium Z2和Protium X2。

靈活應用AI晶片/資料中心CPU

對於Cadence系統動力雙重奏可以結合具體需求使用。以兩大典型的晶片類別―AI晶片和數據中心處理器為例,張永專表示,AI晶片更注重與演算法的結合,不斷反覆運算。在這樣的情況下,晶片在初期開發除錯時,可能50%的時間進行硬體模擬加速,50%的時間進行原型模擬,因為它需要進行大量的向量運算、張量運算等。

資料中心的CPU處理器,不論是x86、Arm或是RISC-V架構,更注重晶片的效率和能耗。可能80%的時間用硬體加速,20%的時間進行作業系統。因此,在實際使用中,Palladium Z2和Protium X2所使用的時機、比例是不一樣的,目標是效率最大化。

目前AI晶片正處在快速的發展週期中,晶片架構不斷演進,不同類型的AI晶片也進一步提升設計難度。Palladium Z2和Protium X2介面種類齊全、相容性高,可支援AI晶片設計並縮短週期,這可能會是在AI晶片市場的競爭優勢。

大約兩年前,Cadence提出智慧系統設計戰略。系統動力雙重奏作為該戰略的一部分,已融入智慧化的特點。它們可將驗證數據收集到Cadence vManager系統中,讓工程師可以直接看到專案進展,透過AI配合大數據驗證效率最大化。在這過程中,Palladium Z2和Protium X2採用獨特的記憶方式,可快速應用於FPGA、GPU、CPU等不同晶片架構。目前,NVIDIA、AMD、Arm、賽靈思(Xilinx)等公司,都已公開證實Cadence系統動力雙重奏的矽前硬體除錯及軟體驗證能力。

晶片設計引領趨勢

晶片設計從規模複雜性到系統複雜性的轉變,伴隨著晶片、系統和軟體的深度融合,半導體產業各個環節都在這一趨勢下發生變革。此外,還有軟硬體的協同設計、驗證,已經向更為早期的階段滲透。這是半導體新週期下,產業面臨的共同挑戰。

開發者在需求定義階段即需軟硬體協同開發,才能得到期望的功能和效能。現階段最需要的就是通用、一致的工具流程,能夠説明他們優化功能驗證、功能確認和矽前軟體初啟的工作負載分布;同時,更大的系統容量也成為複雜晶片設計、驗證的必須。EDA廠商Cadence正在根據行業週期快速升級,來應對呈指數級上升的系統設計複雜度和上市時間的壓力。

(本文原刊登於與非網EEFOCUS)