Open-Silicon、美普思(MIPS)及Dolphin共同宣布,在一般條件下,成功完成時脈超過2.4GHz的高效能特定應用積體電路(ASIC)處理器投片。此效能若依照台積電參考流程的時序收斂(Timing Closure)簽核條件來評比,是目前市場上頻率最高的ASIC處理器,充分展現出這三家業者具備開發高效能處理器的技術。此高效能ASIC處理器是Open-Silicon與美普思(MIPS)繼去年底宣布完成65奈米、1.1GHz測試晶片後的延續性測試晶片開發計畫。

Open-Silicon執行長暨總經理Naveed Sherwani博士表示,Open-Silicon、美普思與Dolphin合作開發這款ASIC處理器,證明三家公司的設計能力及此合作模式的實力。處理器效能最佳化是下一代系統單晶片(SoC)及ASIC的重要需求。這三家公司將持續投入強化處理器設計能力,包括MAX科技公司,以為客戶提供最佳的定製矽晶技術。

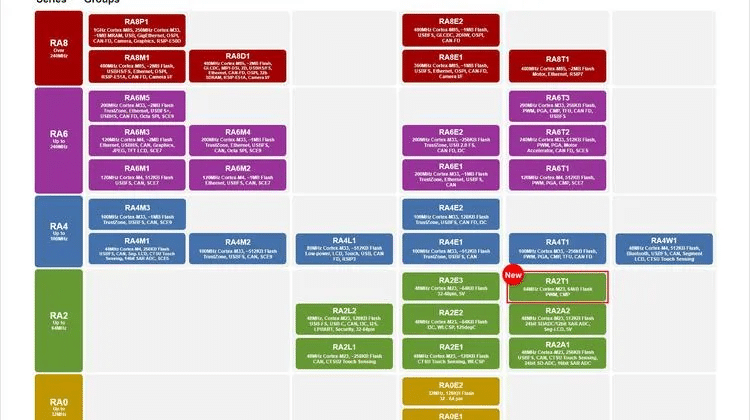

美普思執行長暨總經理Sandeep Vij表示,該公司74K核心已廣泛用在數位家庭、寬頻與無線網路應用中,是市場上唯一具有15級管線的可授權中央處理器(CPU)核心矽智財(IP),同時可提供該公司現有產品組合中最高的單核心效能。74K核心是在40奈米測試晶片上展現優異效能的理想方案,該公司非常高興透過與Open-Silicon及Dolphin的共同合作,能達成超過2.4 GHz的速度,此成果優於其他40奈米、甚至28奈米製程的IP技術。

Dolphin執行長Mo Tamjidi表示,該公司是一間成立超過16年的矽智財供應商,一直致力於協助合作夥伴與客戶達成設計目標。完成40奈米製程的突破性2.4GHz以上效能,展現Dolphin、美普思及Open-Silicon工程團隊的優異經驗。

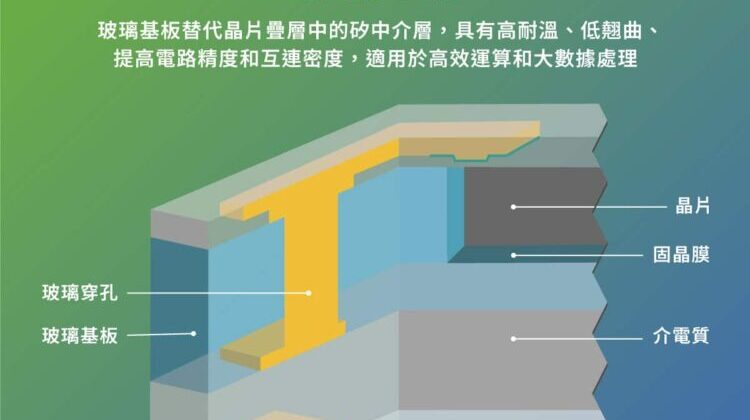

此元件中包含MIPS32 74Kf處理器核心,這是一款超純量、亂序(Out Of Order)CPU,具備高效能整合式浮點運算單元(FPU)、數位訊號處理器(DSP)延伸指令、32K L1快取與32K L1資料快取,以及晶片上(On-chip)8K PDtrace記憶體緩衝器。MIPS32 74K核心是可完全合成的授權IP核心,具備可實現最高頻率的15級管線,已廣泛用在高階數位消費裝置、機上盒及家庭網路方案中。與先前的65奈米設計相同,此晶片的RTL設計是由美普思負責,由Open-Silicon利用Dolphin的記憶體技術完成晶片建置。台積電透過其晶圓光罩共乘服務系統(CyberShuttle)原型計畫製造這款晶片。

為了最佳化效能,Open-Silicon採用其CoreMAXTM技術,以作為特定設計庫的補強。針對此設計,Open-Silicon開發159個新的LVt單元及147個RVt與HVt單元,用來最佳化MIPS 74Kf核心與FPU間的關鍵路徑。其他實體設計技術包括Open-Silicon的優異處理器平面規畫(Floorplanning)、時脈樹合成及時脈驅動的布局最佳化。實體設計則是採用Cadence 的EDA布局工具。

美普思網址:www.mips.com

Open-Silicon 網址:www.open-silicon.com

Dolphin網址:www.dolphin-ic.com