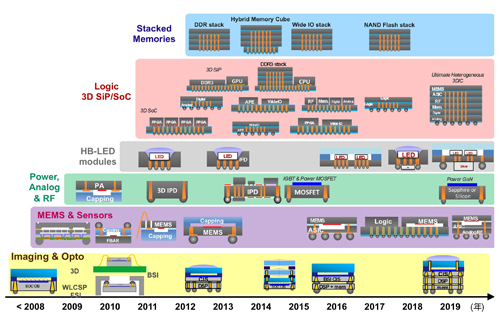

三維晶片(3D IC)關鍵製程技術大躍進。為加速3D IC量產,半導體設備商除積極布局矽穿孔(TSV)製程外,亦加緊部署後段矽穿孔露出(Via-Reveal)技術,助力優化晶片堆疊組裝效率,目前包括應用材料(Applied Materials)和SPTS均已提出解決方案,全力卡位。

|

| 應用材料TSV/先進封裝戰略暨行銷總監Sesh Ramaswami(右)認為,3D IC雖為半導體設備商帶來不少技術挑戰,但也同時引爆新商機,應用材料將以領先的TSV技術積極卡位。左為應用材料企業副總裁暨全球半導體業務事業服務群總經理余定陸 |

應用材料TSV/先進封裝戰略暨行銷總監Sesh Ramaswami表示,該公司已與新加坡微電子研究院(IME)共同投資超過1億美元,在新加坡設立先進封裝卓越中心,透過一條完整的12吋晶圓實驗線強攻3D IC封裝技術。應用材料現已將五款以上既有設備改良成適合TSV製程應用的版本,並特別針對Via-Reveal製作需求,打造一套囊括乾式蝕刻(Etching)、化學氣相沉積(CVD)和化學機械研磨(CMP)的完整解決方案。

據了解,Via-Reveal亦稱為後TSV(Post-TSV)製程,係在晶圓正面完成矽穿孔後,利用CMP機台進一步將晶圓背面磨薄5~10微米,以利進行乾式蝕刻,使填充銅材料的矽穿孔露出約5微米高度,並在末端進行電介質鈍化(Passivate);隨後再以CMP拋光,進而暴露出銅材料供重新分配層(RDL)金屬化之用,以便連接晶圓錫球(Wafer Bump),為3D IC堆疊做好準備。

Ramaswami坦言,3D IC發展初期,包括半導體設備商、晶圓代工及封測業者均著眼於TSV研發,輕忽晶圓穿孔後須在背面執行Via-Reveal的製作問題;隨著TSV技術日益成熟,提升Via-Reveal效率的重要性正與日俱增,該技術的成熟度將成為加速3D IC問世的關鍵指標。

為協助封測業者及早完成3D IC製程部署,Ramaswami透露,應用材料不僅發展出業界獨有的乾式蝕刻、CVD加CMP一站式Via-Reveal方案,讓客戶能迅速投入生產;也攜手台灣研究機構,埋首研發整段3D IC製程的各環節優化方案,從而提升生產效率並降低投資。同時,應用材料亦追求性能更加出色的材料,如以玻璃取代矽基板的方式,提升3D IC在高頻率運作時的表現。

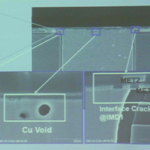

無獨有偶,半導體製造方案供應商–SPTS日前亦於2012年國際半導體展(SEMICON),揭露新一代Via-Reveal製程設備。該方案提供更快的晶圓蝕刻速率,並能使12吋TSV晶圓接合(Bonded)均勻度達±2.5%;同時也導入業界唯一Via-Reveal終點偵測(Endpoint)系統,有助強化3D IC良率。

SPTS蝕刻產品行銷總監Dave Thomas認為,蝕刻速率、均勻度控制和終點偵測,係實現Via-Reveal製程中,降低單位晶粒成本與提高良率的主要因素。透過SPTS創新的雙電漿源反應爐設計,再結合一套終點偵測技術,將一舉突破3D IC封裝層層阻礙。

顯而易見,半導體設備廠針對TSV、Via-Reveal開發的解決方案相繼到位,再配合3D IC標準組織、晶圓代工、封測廠及處理器開發商持續加碼挹注資源,3D IC生態系統正快步成形。Ramaswami也預期,3D IC將於2~3年內放量,大舉搶進高階行動裝置、雲端設施、影像與網通設備等應用領域,讓產品效能與功耗規格更上層樓。