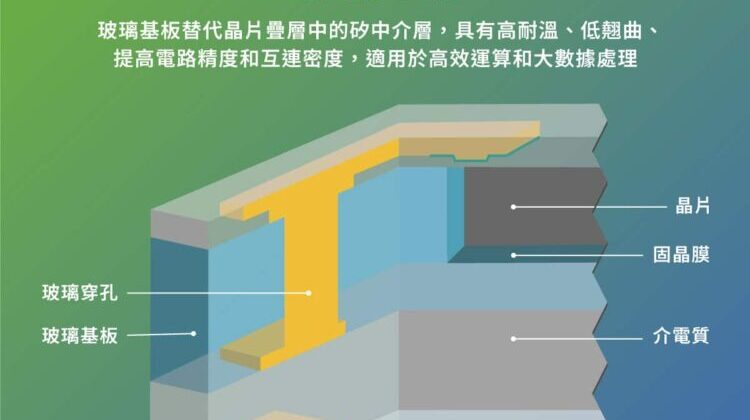

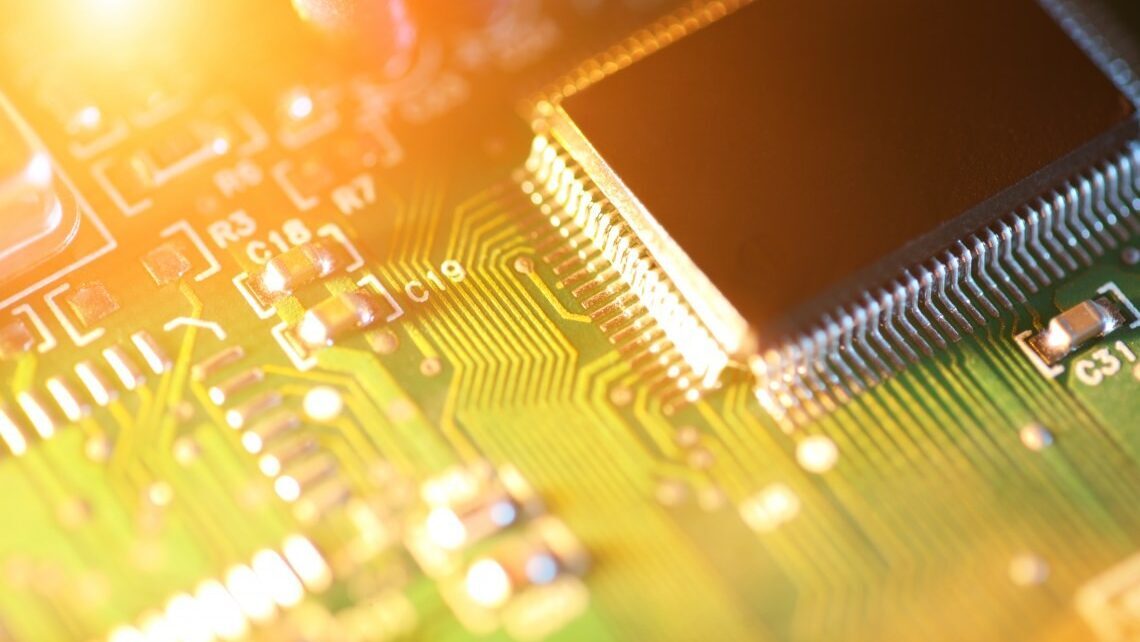

封裝技術已逐漸凌駕晶圓製程技術,成為未來半導體功能整合時不可或缺的關鍵能力。尤其在超越摩爾定律(More than Moore)與異質整合等新發展思潮的帶動下,包括三維晶片(3D IC)與矽穿孔(TSV)等先進封裝技術更是半導體製造商與IC設計業者戮力布局的新重點。

|

| IMEC總裁暨執行長Luc Van den hove表示,未來10年3D技術在半導體發展上將扮演重要角色。

|

IMEC總裁暨執行長Luc Van den hove指出,不論是現今最熱門的嵌入式連網或漸趨重要的醫療照護、無線感測網路、生命科學與實驗室晶片(Lab on a Chip)等應用,均須整合不同功能的晶片來達成,因此利用3D方式將記憶體、邏輯、微機電系統(MEMS)等異質晶片整合的技術已不可或缺。

有鑑於此,IMEC除持續發展極紫外光(EUV)微影(Lithography)等先進製程技術以追求更高電晶體整合,達到「更多摩爾(More Moore)」的發展目標外,亦致力於MEMS、感測器、生物電子、光子(Photonic)與光學偵測器(Optical Detector)等元件的開發與整合,朝向「超越摩爾(More than Moore)」的方向邁進。

隨著先進半導體製程研發費用急遽攀升,可負擔如此高昂研發成本的半導體公司也愈來愈少,因而讓利用封裝技術實現更多功能整合的設計取向開始大行其道。事實上,IMEC日前也已成功投產採用TSV與微凸塊(Micro-bump)技術將動態隨機存取記憶體(DRAM)堆疊在邏輯晶片上的3D晶片。

不過,Van den hove也強調,儘管異質整合的重要性已逐漸提升,不過,以電晶體微縮為目標的製程技術仍將是半導體發展的核心基礎,該公司將兼顧「More Moore」與「More than Moore」的相關技術,以因應半導體未來10年的創新發展趨勢。