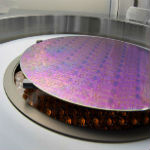

台積電20奈米(nm)及三維晶片(3D IC)設計參考流程出爐。台積電日前正式宣布推出20奈米製程,以及應用於3D IC生產的CoWoS(Chip on Wafer on Substrate)兩項設計參考流程,以維持旗下半導體製程技術領先競爭對手半年到1年的腳步,防堵格羅方德(GLOBALFUNDRIES)、聯電的技術追趕。

台積電研究發展副總經理侯永清表示,台積電在開放創新平台(Open Innovation Platform, OIP)架構中,支援20奈米與CoWoS製程的設計環境已準備就緒;並已發展兩套先進設計參考流程,將助力IC設計業者加速切入20奈米及3D IC設計。

事實上,近期晶圓代工廠在先進製程的炮火已日益猛烈。其中,格羅方德不僅宣稱已拿下超過百件28奈米設計定案(Tape Out),且今年上半年營收也擠下聯電,成為全球第二大晶圓代工廠。此外,格羅方德近期還揭露一項新計畫,預計在2014年以3D鰭式電晶體(FinFET)打造14奈米與20奈米混合製程–14nm-XM技術,足見其擴張事業版圖的企圖心。

至於聯電則致力擴充40、28奈米產能搶市,並已取得IBM的20奈米、FinFET技術授權,加緊布局先進製程;同時,也正緊鑼密鼓部署3D IC矽穿孔(TSV)量產服務。據了解,今年第四季聯電28奈米製程營收,可望達到該公司整體營收5%的水準,未來幾年也將在20奈米以下製程領域大顯身手,搶占市場商機。

侯永清指出,對台積電及其開放創新平台設計生態環境夥伴而言,首要目標在於能及早催生先進的矽晶片生產技術,以協助終端客戶打造功能更出色的產品。隨著台積電勾勒出20奈米先進製程與3D IC生產製造模式,對實現此一目標將大有助益。

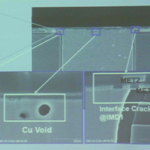

台積電20奈米參考流程已經過驗證,將提供客戶雙重曝光技術(Double Patterning Technology, DPT)所需的布局與配線(Place and Route)、時序(Timing)、實體驗證(Physical Verification)、可製造性設計(DFM)及電子設計自動化(EDA)工具等知識,協助客戶順利以台積電20奈米製程開發新一代晶片,並降低設計複雜度及提高精確性。

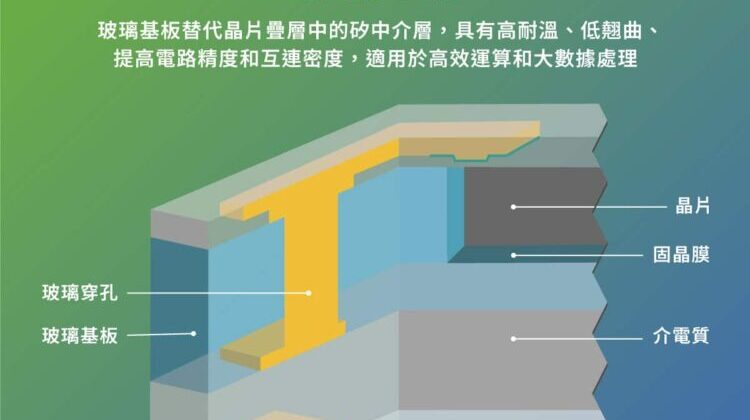

另一方面,台積電CoWoS參考流程亦通過矽晶片驗證,可順利整合並堆疊異質晶片,以因應高頻寬、低功耗產品設計需求;同時讓晶片商受惠於現成的EDA工具、晶片連接訊號一致性、熱分析,以及晶片級(Die-level)與堆疊級(Stacking-level)測試所需的整合式3D IC電路測試方法,加速產品上市。