半導體設備、封測廠今年將擴大高階覆晶封裝(Flip Chip)研發支出。隨著半導體開始邁入3D IC架構,晶片封裝技術也面臨重大挑戰,因此一線半導體設備廠、封測業者皆積極布局高階覆晶封裝,並改革相關技術、材料,期配合矽穿孔(TSV)製程發展,實現3D IC商用。

|

| 應用材料半導體事業群金屬沉積產品全球產品經理歐岳生認為,半導體製程微縮須與封裝技術同步演進,才能真正發揮效能提升、功耗銳減的效益。 |

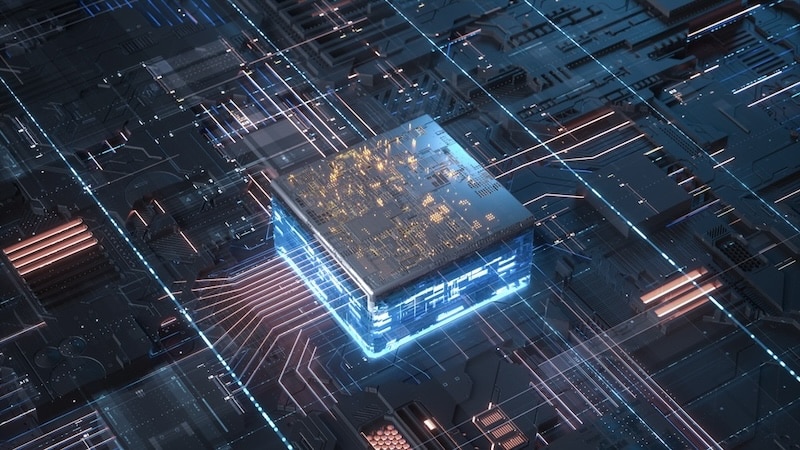

應用材料(Applied Materials)半導體事業群金屬沉積產品全球產品經理歐岳生表示,以往半導體封裝技術的重要性不如製程演進,然而,隨著晶片設計益趨複雜,所搭配的封裝製程難度也同步提高;尤其步入2.5D/3D IC時代後,晶圓代工及封測業者為讓晶片在不影響占位空間的前提下,順利向上堆疊並協同運作,第一步就是要導入先進晶圓級封裝(WLP)、覆晶封裝技術,以打造優良的錫球下層金屬(Under Bump Metallurgy, UBM)並鞏固3D IC底層結構。

歐岳生指出,目前半導體產業陷入將3D IC與矽穿孔劃上等號的迷思,認為只要該技術完備就能量產3D IC;但實際上,開發3D IC包含許多道工序,首先晶圓代工業者須完成晶圓薄化,並以矽穿孔製程鑿穿晶圓進行堆疊,後續則須借重封測廠導入高階覆晶封裝,讓銅柱(Pillar)、晶圓錫球(Bump)在更小的晶圓開孔中接合,並克服薄晶圓可靠度、應力和低介電材料損壞(Low K Damage)等問題,才能順利將產品推向市場。

由此可見,封裝技術之於3D IC製造,重要程度並不遜於矽穿孔製程,並將成為實現3D IC的臨門一腳。歐岳生也透露,應用材料正攜手台灣一線封測業者,透過其在新加坡設立的先進封裝技術中心,積極提升半導體覆晶技術;同時也致力改良化學氣相沉積(CVD)、物理氣相沉積(PVD)等設備,協助半導體製造商布局高階製程與覆晶封裝方案。

與此同時,因應薄晶圓製程在高溫貼合或剝離聚合物(Polymer)時,常面臨彎曲、不均勻等問題,應用材料也快馬加鞭研發低溫聚合物材料,以提高薄晶圓可靠度與穩定性,避免溫度影響品質。

據市場研究機構Prismark預估,高階覆晶封裝產值可望從2011年的97億2,000萬美元成長到2016年的157億7,000萬美元。現階段,包括日月光、艾克爾(Amkor)、矽品和星科金朋(STATS ChipPAC)、力成等全球前五大封測廠,均開始衝刺高階覆晶封裝產能,2013年預期將再擴大資本支出,卡位28、20奈米(nm),以及3D IC封裝市場商機。