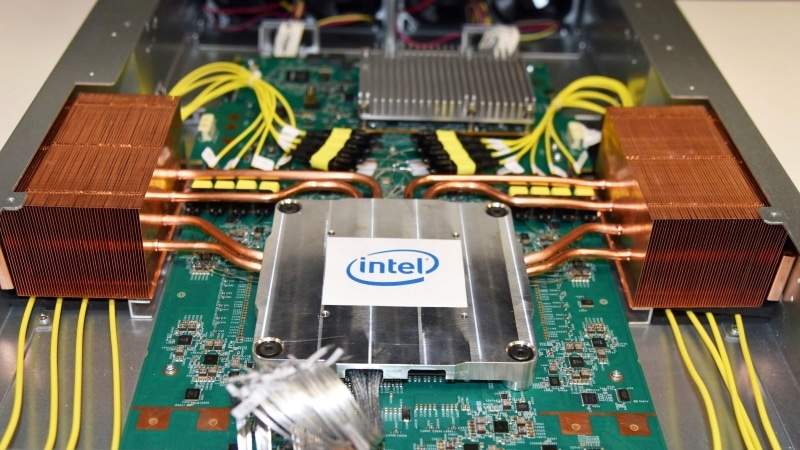

這項技術能夠將不同組織設計的專用元件整合到單一設計中,在效能、功耗、佔位面積和成本方面實現SoC無法達到的改善。然而,從傳統SoC設計跳躍到3D IC設計,不僅帶來新機會,也伴隨全新挑戰。

Chiplet已成為描述專為特定功能設計之裸晶的新興術語,可整合至3D IC設計中並使用矽中介層互連。3D IC設計能夠實現效能、功耗、佔位面積和成本的改善,這些都是傳統SoC和IC設計無法達到的水準。垂直chiplet堆疊為自動化繞線工具帶來新挑戰,從物理驗證角度來看,更打破了傳統製程設計套件(PDK)的基本架構概念。

垂直堆疊突破二維限制 chiplet整合重新定義設計

傳統物理驗證工具從二維(2D)角度檢視設計資料。雖然各層間可能存在隱含的垂直區別,但同一層上重疊或相接的幾何圖形會被視為代表單一形狀。在3D IC設計中,chiplet設計師無法依賴這種2D方法,因為他們根本不知道在3D IC設計中可能會有什麼元件垂直堆疊。一個chiplet中某層的幾何圖形若與另一個垂直放置的chiplet中的幾何圖形重疊,不能也不應該被視為單一形狀。

單一設計中異質製程的支援也造成問題。PDK依賴層映射來啟用各層的個別檢查。在3D IC中,代工廠或外包組裝測試(OSAT)公司不可能知道3D IC設計師可能想要整合的任何chiplet相關的所有特定層和規則,因為每個chiplet可能與不同的製程技術相關聯。這些根本性挑戰需要全新的解決方案。

Calibre 3DSTACK破解驗證困境 自動化流程提升效率

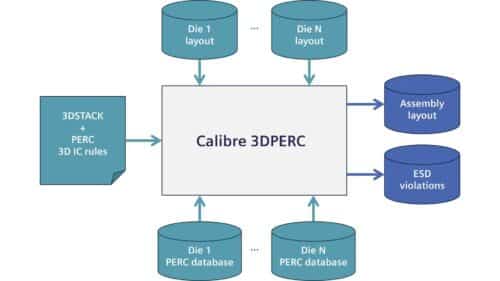

電子設計自動化(EDA)產業已經開始提供解決方案。Siemens EDA的Calibre 3DSTACK工具是專門用於在異質3D IC組裝中執行設計規則檢查(DRC)和佈局與電路圖比對(LVS)驗證的專用解決方案。Calibre 3DSTACK流程從擷取設計特定資訊開始,例如每個chiplet的層映射和放置資訊。

設計師可以手動以ASCI I檔案的形式提供此資料,或者可以使用Siemens的Xpedition Substrate Integrator(xSI)虛擬原型環境自動化擷取,該環境允許設計師規劃和原型化各種整合方法,以及指定元件之間的連接性。透過這些資訊,設計師不僅可以使用xSI工具驅動傳統佈局繞線(P&R)解決方案或封裝佈局解決方案的水準和垂直設計整合自動化,還可以自動化建立Calibre 3DSTACK指令檔並建立預期的來源網表。

使用每個chiplet的層映射和放置資訊,Calibre 3DSTACK工具可以自動為每個chiplet的每一層建立唯一識別,避免任何可能的衝突,同時仍然能夠透過在所有chiplet之間提供跨通用層類型的抽象層命名來指定所需規則。該工具自動實施每個主動晶片的灰盒方法,同時提取必要的晶片間或晶片至球閘陣列(BGA)連接。

多重物理分析需求攀升 熱應力管控成關鍵考量

3D IC設計的另一個挑戰包括額外類型的分析。熱應力和機械應力可能對主動裝置和金屬互連的電氣行為產生有害影響。在SoC中,這些風險較不顯著,可以透過結合DRC和LVS檢查與標準功率、電遷移(EM)和電壓(IR)降分析來大幅減輕。由於元件的異質性質和垂直堆疊的存在,這種解決方案在3D IC設計驗證中並不充分。

設計團隊可以使用與Calibre 3DSTACK chiplet唯一識別中使用的相同技術來解決3D IC設計中的這些挑戰,包括透過xSI工具的自動化。設計師可以評估所有元件的3D IC功率域。他們可以透過結合Siemens Simcenter Flotherm技術與Calibre引擎的熱分析解決方案,生成準確的靜態或動態溫度圖,為靜態或動態提取完整3D IC組裝生成準確的chiplet級熱模型。

類似地, 新的機械應力影響,包括來自BGA、矽穿孔(TSV)、堆疊晶片等的影響,都可以在3D IC組裝層級擷取,能夠建立應力色彩圖,設計師可以使用這些色彩圖生成chiplet/晶片特定的提取網表,其中裝置被註解以說明電晶體級的遷移率變化。熱應力和機械應力分析的結合產生高度準確的結果,可以被擷取並用於電路模擬。

自動化整合加速設計週期 迭代分析降低風險

透過自動化和整合,設計師現在可以在不同細節層級進行迭代分析。對於初始規劃,他們可以使用xSI工具生成多種可能的設計方法。透過將chiplet視為具有均勻功率的均勻區塊,設計師可以快速了解不同堆疊方法可能受到的影響。隨著每個chiplet、中介層和/或基板的更多資訊變得可用,他們可以執行進一步的迭代以獲得更高的準確性。

修復選項,例如在chiplet中添加堆疊過孔或TSV以幫助散熱,可以應用於後續驗證中的包含。這個過程可以重複進行,直到最終組裝完成,使設計師能夠減少每個迭代層級所需的修改數量,並降低在最終投片時發生關鍵效能、可靠性和製造問題的風險。

雖然3D IC為電子市場帶來巨大前景,但也帶來必須預先解決的新挑戰,以確保足夠的設計良率和可靠性。異質晶片或chiplet整合到有機材料中並以新的垂直和水平方法連接,會在散熱和機械應力方面產生新問題。考慮這些影響不僅需要封裝級分析,還需要將晶片特定細節整合到裝置級,以適當確保完整的設計電氣合規性。Siemens EDA提供經過驗證的設計到驗證和分析解決方案,透過連接xSI規劃工具到佈局自動化、3D物理驗證、功率分析、熱分析、機械分析和EM/IR分析,實現早期設計階段問題的識別和修正,並確保準確的物理和電氣行為驗證。

(本文作者為西門子Calibre 3D IC產品總監)