IC設計與封裝設計的界線越來越模糊,台積電的InFO封裝技術,更讓許多專業封測廠捏了把冷汗。目前台積電InFO封裝所搭配的主要EDA工具由益華電腦(Cadence)提供,雙方有很深入的合作夥伴關係,不過,Cadence並未獨厚台積電,同時也正與日月光、矽品等專業委外封測廠(OSAT)攜手發展與InFO類似的Fan-out Wafer Level Packaging(FO-WLP)設計工具。

針對台積電InFO設計,Cadence近期推出新的整合流程及一系列工具,將提供行動通訊及IoT應用的設計及分析能力,和跨晶粒(Cross-die)互動建模。該流程可協助系統單晶片設計人員,於單視窗支援多種製程結構環境下,快速將全系統的多晶粒及InFO封裝中產生網路列表,並直接自封裝設計資料庫,產生標準寄生交換格式(Standard Parasitic Exchange Format, SPEF),大幅簡化時序簽核。

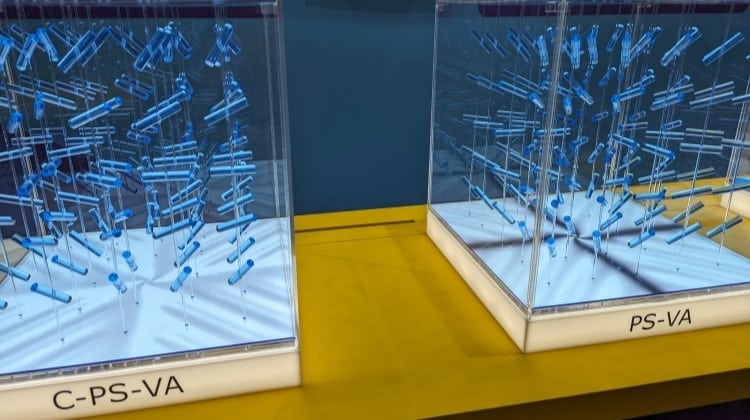

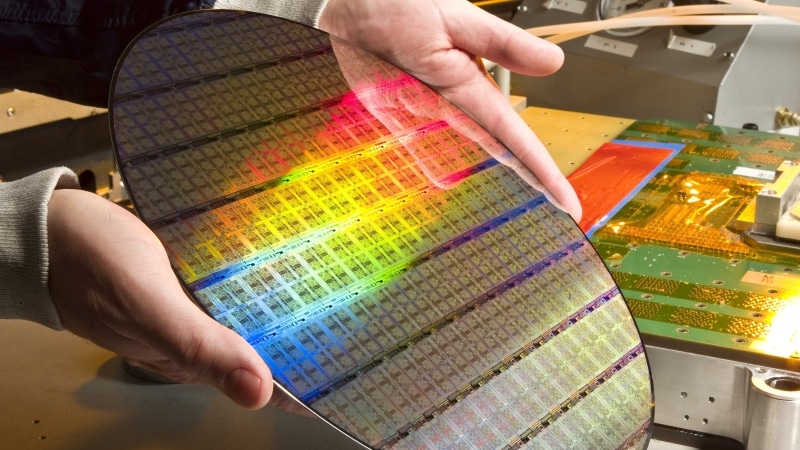

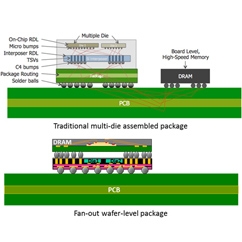

Sigrity研發部門資深總監An-Yu Kuo表示,InFO與一般封裝技術最大的不同在於,以往的封裝屬於小型印刷電路板製程,InFO則已完全採用晶片製程,是封裝技術發展上的重大突破,且InFO還能使晶片更小、更薄,因此前景備受看好,像是蘋果的iPhone7、7Plus處理器,便採用InFO封裝。

由於InFO必須要靠IC前後段製程無縫整合才能實現,因此勢必將對封裝廠產生很大的衝擊。為此,包含日月光、矽品、艾克爾(Amkor)等國際一線封測大廠,也都在發展自己的FO-WLP技術。事實上,Cadence除了和台積電有很深的合作關係外,同時也正與眾家專業封測廠合作,共同發展FO-WLP設計工具。然而,每家廠商的技術都是獨特的,最後產出的晶片型態也有差異。因此,Cadence推出的設計解決方案,必然是高度客製化的工具。Cadence在技術保密的部分,相當受到台積電信任。

An-Yu Kuo進一步表示,日月光、矽品在FO-WLP也都有相當的投入。一旦當封測廠的客戶開始採用FO-WLP,也將進而推動Cadence EDA相關設計工具的需求。當晶圓製造/封裝廠的製程有所更動,Cadence的設計工具也必須很快地跟上,因為EDA產業的價值,就是幫客戶解決他們在產品設計開發上所遇到的種種問題。FO-WLP的情況也是如此,主要是由客戶來指定Cadence推出相關設計工具,而不是Cadence推出一套工具,來解決所有客戶的問題。

目前InFO主要應用在高階晶片,未來能否進一步向下滲透,成本將是很大的關鍵。An-Yu Kuo指出,現今InFO主要應用於高階晶片,但若要向下滲透,將有兩大關鍵,一是InFO製程的良率,二是設計的成本。前者與晶圓廠、封裝廠有關,後者則是Cadence能著力的部分。InFO會讓封裝設計必須跟IC設計更緊密結合,其結果就是封裝設計的複雜度大幅提升,而讓相關流程變得更簡單、更自動化,自然是EDA供應商的責任。