IC尺寸日趨精緻、效能要求不減反增,礙於物理上的限制,不得不向2.5D、3D或扇出型晶圓級封裝(FO-WLP)等高密度先進封裝(HDAP)形式發展。針對此類接腳(Pin)數超過1萬、傳統工具難以因應的封裝設計,明導國際(Mentor)以Xpendition為基礎,6月中旬推出整合設計、Layout與多重檢驗工具的完整解決方案;同時與艾爾克(Amkor)等委外封裝測試(OSAT)廠商合作、推動Mentor OSAT聯盟計畫,力圖降低進入門檻、帶動整個生態系成長。

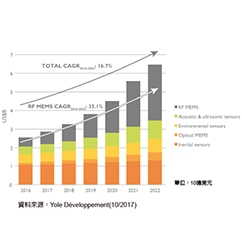

先進封裝技術研調機構TechSearch總裁Jan Vardaman預測,FO-WLP在2015至2020年間將有高達82%的驚人成長率,將為傳統設計/製造供應鏈帶來極大衝擊;伴隨其他HDAP技術進展,可望催生元件與封裝的整合設計,以及相應解決方案的需求。近年摩爾定律陷入瓶頸,行動裝置、車載系統等高端應用發展卻不見停歇,為持續追求更高效能、降低體積與成本,Mentor也認為HDAP將在10年內成為市場主流。

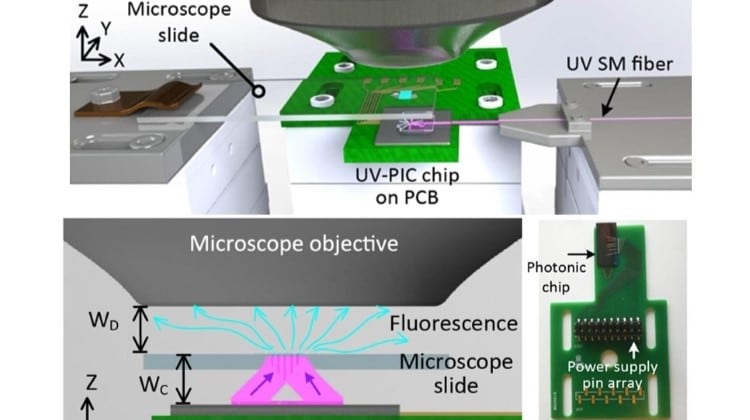

封裝設計邁入3D不僅提高複雜度、令設計工具效能要求提高,考慮到晶片堆疊導致的成本倍增,Mentor市場發展經理Jamie Metcalfe強調HDAP相當經不起浪費,設計上需要極高可靠度。為此,Mentor新方案整合流程中所需各類工具,廠商可在進行封裝與印刷電路板(PCB)設計時同步交換資訊,並圖像化呈現晶片、球柵陣列封裝(BGA)、PCB間的連接關係,除方便觀察、強化整體效率,也為減少錯誤與不契合的狀況發生。

再者,廠商可藉內建設計規則驗證(DRC)機制,於設計過程中先行除錯,在交付前找出絕大部分問題;透過內建快速建模功能,可迅速生成3D封裝模型,以便進行訊號完整性(SI)、電源完整性(PI)等相關驗證。最後輸出GDSII數據後,則可利用Calibre做最後把關,進行電路布局驗證(LVS)、布局對布局驗證(LVL)等實體檢驗,並能即時標錯、同步開始修正,無須中斷當下的檢驗流程。

此方案亦支持異質資料庫,以便整合AIF、CSV等不同數據格式,協助廠商進行更快速、更大量的設計作業。

另一方面,鑑於台積電力推整合扇出型(InFO)封裝、在HDAP領域來勢洶洶,Mentor近期亦發表其OSAT聯盟計畫。該聯盟以Amkor為首位成員,並邀請日月光、矽品等主力廠商,力圖強化整體競爭力。藉此,Mentor期望透過成員間的合作,為其客戶或無晶圓IC設計的其他公司開發HDAP相關設計套件、認證工具等,降低進入成本與風險以利推廣,帶動整個生態系向上成長。